#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

Disclaimer 🖃

## 工學碩士 學位論文

초전도 에너지 저장 장치용 3상 사이리스터 브리지의 비대칭 제어에 관한 연구

A Study on the asymmetric control of 3-phase thyristor bridge for Superconducting Magnet Energy Storage (SMES)

指導教授 金 潤 植

2018年 8月

韓國海洋大學校 大學院

電氣電子工學科

金 承 賢

## 本 論文을 金承賢의 工學碩士 學位論文으로 認准함

委員長:工學博士 李 成 根 即

委 員:工學博士 吉 暻 碩 即

委 員:工學博士 金 潤 植 即

2018年 6月

韓國海洋大學校 大學院

電氣電子工學科

金 承 賢

## 목 차

| ユ  | 림 '  | 및 표              | 목차            |                                                       | ii |

|----|------|------------------|---------------|-------------------------------------------------------|----|

| Ab | stra | ct               | •••••         |                                                       | v  |

|    |      |                  |               |                                                       |    |

| 제  | 1    | 장 서              | اِ اِ         | 론                                                     | 01 |

| 1Ì | •    | יא וכ            | 1 :           | =                                                     | 03 |

| 셰  | 2 -  | გ <del>ი</del> ი |               | 론<br>지 저장 시스템(SMES) ///////////////                   | 03 |

|    | 2.   | 1 초전되            | 도 에너?         | 지 저장 시스템(SMES)<br>브리지 제어                              | 03 |

|    | 2    |                  |               |                                                       |    |

|    |      |                  |               | 제어 (Symmetry control)                                 |    |

|    | 2    | 2.2.2<br>2 계하    | 비내성<br>제 ml a | ! 제어 (Asymmetry control) ······<br>출력전압 및 출력전류 ······ | 13 |

|    |      |                  |               | 브리지의 비대칭 제어 동작 특성                                     |    |

|    | ۷.   |                  |               | _ 다시다 하대 0 시 1 0 기 기 0<br>  겹침과 전환각                   |    |

|    |      | 2.4.2            | 동시전           | [환과 전환실패                                              | 30 |

|    | 2.:  | 5 역률             | 및 고조          | 스파                                                    | 44 |

|    |      | ·                |               |                                                       |    |

| 제  | 3    | 장 초              | 전도            | 에너지 저장 장치용 전력변환기                                      | 47 |

|    | 3.   | 1 초전!            | 도 에너          | 지 저장 장치용 전력변환기                                        | 47 |

|    |      |                  |               |                                                       |    |

|    | 3    | 3 시뮬             | 페이션 :         | 및 실험                                                  | 51 |

|    |      |                  |               | 모드 (Converter mode) ······                            |    |

|    |      |                  |               | 모드 (Inverter mode) ·····                              |    |

|    | 3.4  | 4 결과             | 및 고칠          | 랄                                                     | 58 |

| 제  | 4    | 잣 겯              | ] _j          | 론                                                     | 59 |

| -  |      | _                |               | 헌 ····································                |    |

| Ή  | -    | <u> </u>         | ፈ_ `          | i.                                                    | υU |

## 그림 및 표 목차

| <그림목차>  |                                                                                |  |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------|--|--|--|--|--|--|

| 그림 2.1  | 초전도 에너지 저장 시스템의 에너지 저장 방법04                                                    |  |  |  |  |  |  |

| 그림 2.2  | 3상 사이리스터 브리지 회로 제어06                                                           |  |  |  |  |  |  |

| 그림 2.3  | 제어 방법에 따른 유효전력 $(P)$ 와 무효전력 $(Q)$ 의 관계 $\cdots \cdots 08$                      |  |  |  |  |  |  |

| 그림 2.4  | 컨버터 모드에서의 제어각 변화에 따른 대칭 제어10                                                   |  |  |  |  |  |  |

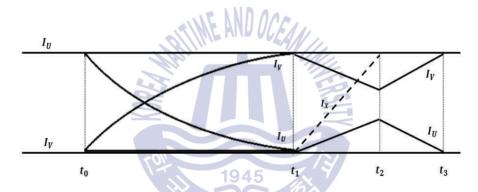

| 그림 2.5  | 인버터 모드에서의 제어각 변화에 따른 대칭 제어13                                                   |  |  |  |  |  |  |

| 그림 2.6  | 컨버터 모드에서의 제어각 변화에 따른 비대칭 제어16                                                  |  |  |  |  |  |  |

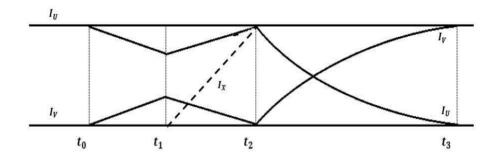

| 그림 2.7  | 인버터 모드에서의 제어각 변화에 따른 비대칭 제어 20                                                 |  |  |  |  |  |  |

| 그림 2.8  | 3상 사이리스터 브리지의 전환 구간 ~~~~~ 26                                                   |  |  |  |  |  |  |

| 그림 2.9  | 사이리스터 U-V 전환 시 제어각 $(\alpha)$ 와 전환각 $(u)$ ···································· |  |  |  |  |  |  |

| 그림 2.10 | 사이리스터 U-V 전환 시 전류 $i_u,\ i_v$ 와 평균 출력전류 $I_d$ $\cdots 28$                      |  |  |  |  |  |  |

| 그림 2.11 | 3상 사이리스터의 동시 전환30                                                              |  |  |  |  |  |  |

| 그림 2.12 | 상전압과 비대칭 제어의 제어각의 관계31                                                         |  |  |  |  |  |  |

| 그림 2.13 | 비대칭 제어에서의 전환 상호 영향 구간33                                                        |  |  |  |  |  |  |

| 그림 2.14 | 입력 리액턴스 $(X_{\mathcal{C}})$ 의 크기과 전환 성공 영역 $\cdots \cdots 34$                  |  |  |  |  |  |  |

| 그림 2.15 | 사이리스터 U-V의 전환 완료와 Z-X의 전환 시 전류 파형…35                                           |  |  |  |  |  |  |

| 그림 2.16 | 사이리스터 U-V의 전환 중 Z-X의 전환 시 전류 파형 36                                             |  |  |  |  |  |  |

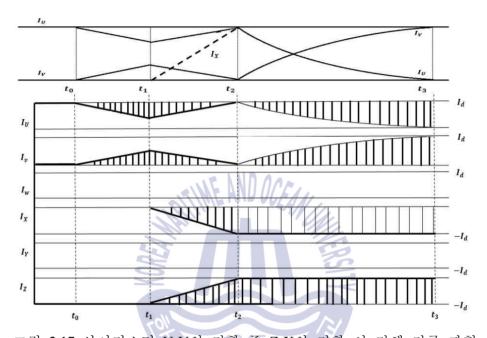

| 그림 2.17 | 사이리스터 U-V의 전환 중 Z-X의 전환 시 전체 전류 파형·37                                          |  |  |  |  |  |  |

| 그림 2.18 | 동시 전환 과정 $(t_0-t_1)$ 회로도와 전체 전류 파형 $\cdots 38$                                 |  |  |  |  |  |  |

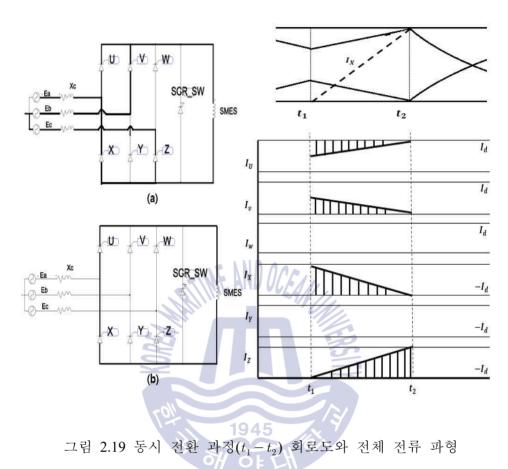

| 그림 2.19 | 동시 전환 과정 $(t_1-t_2)$ 회로도와 전체 전류 파형 $\cdots 39$                                 |  |  |  |  |  |  |

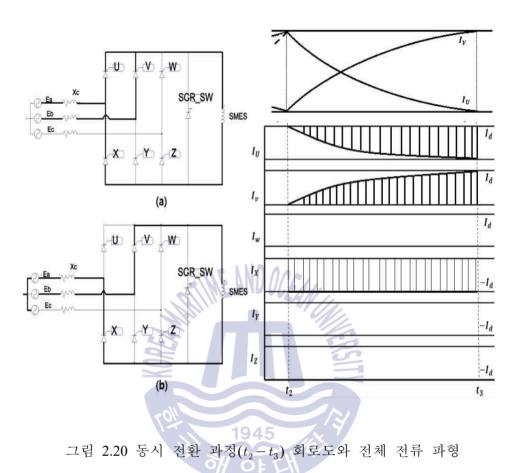

| 그림 2.20 | 동시 전환 과정 $(t_2-t_3)$ 회로도와 전체 전류 파형 $\cdots \cdots 40$                          |  |  |  |  |  |  |

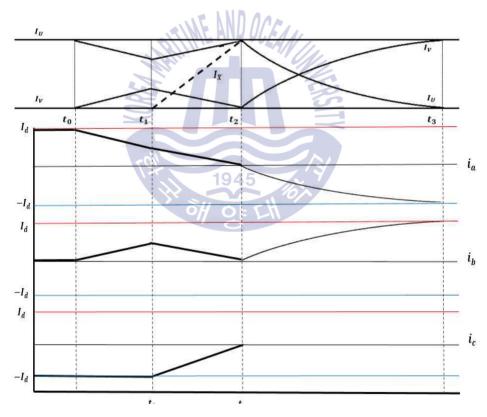

| 그림 2.21 | 사이리스터 동시 전환에서 각 상의 전류 파형41                                                     |  |  |  |  |  |  |

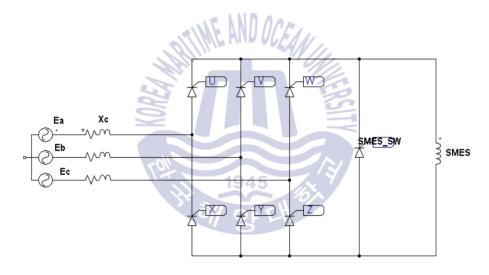

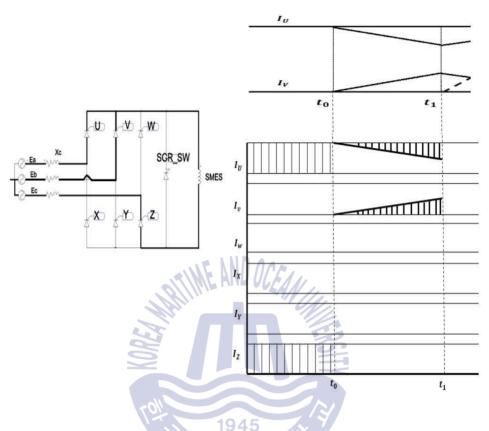

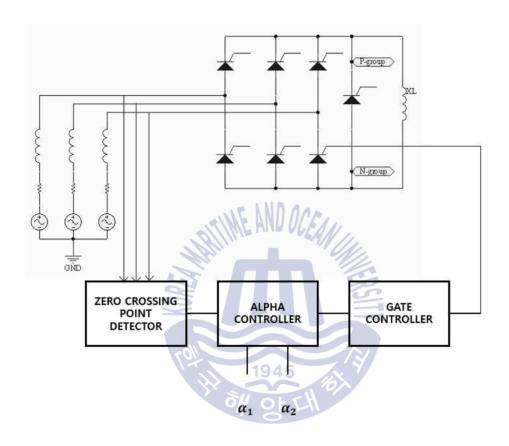

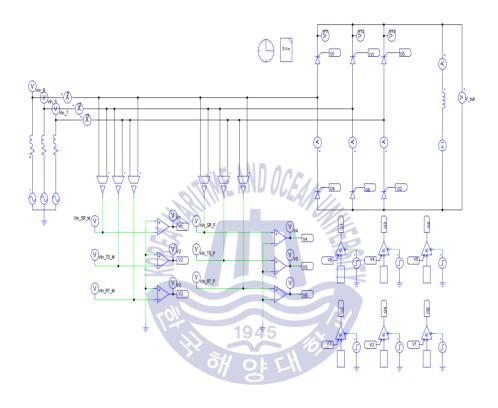

| 그림 3.1  | 초전도 에너지 저장 장치용 3상 사이리스터 브리지 회로 48                                              |  |  |  |  |  |  |

| 그림 3.2  | 초전도 에너지 저장 장치용 3상 사이리스터 브리지 구성 51                                              |  |  |  |  |  |  |

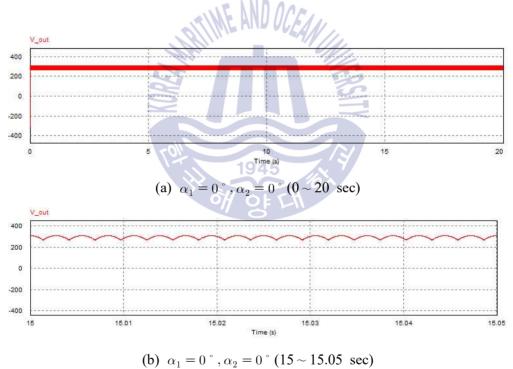

| 그림 3.3  | 컨버터 모드의 대칭 제어 $lpha_1=0^\circ$ , $lpha_2=0^\circ$ 의 출력 전압파형 52                 |  |  |  |  |  |  |

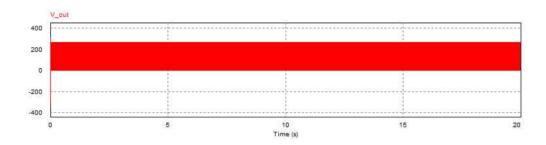

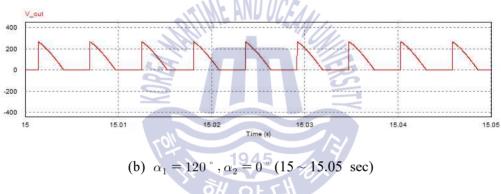

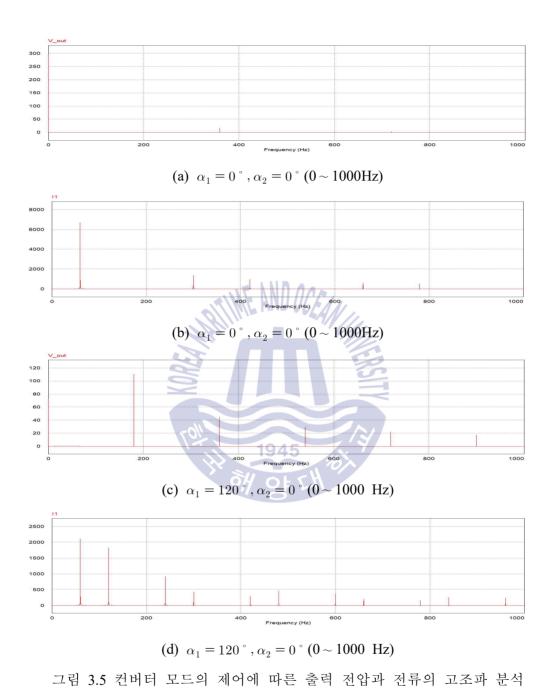

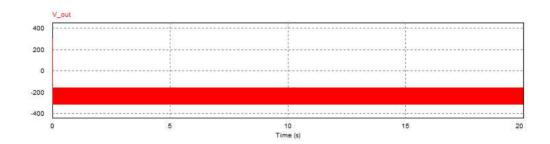

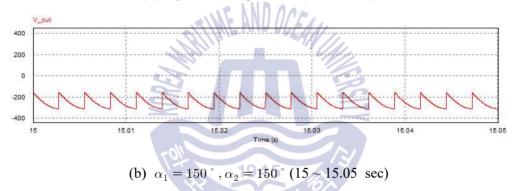

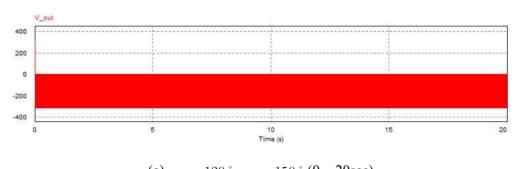

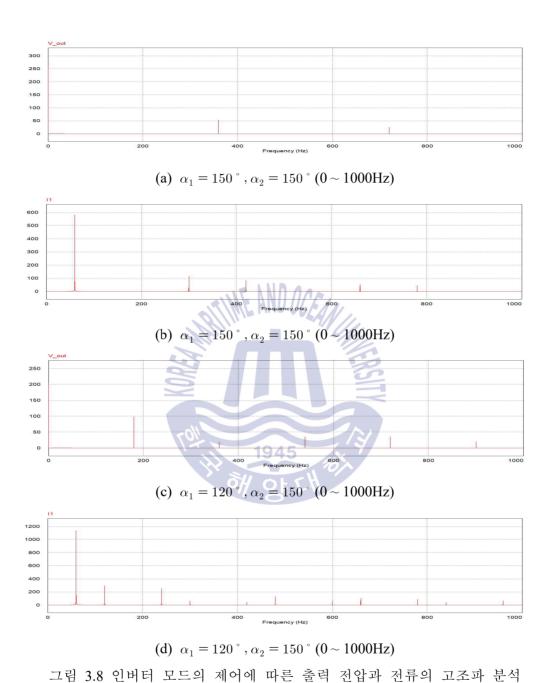

그림 3.4 컨버터 모드의 비대칭 제어  $\alpha_1=120^\circ$ ,  $\alpha_2=0^\circ$ 의 출력 전압 53 그림 3.5 컨버터 모드의 제어에 따른 출력전압과 전류의 고조파 분석 54 그림 3.6 인버터 모드의 대칭 제어  $\alpha_1=150^\circ$ ,  $\alpha_2=150^\circ$ 의 출력 전압 55 그림 3.7 인버터 모드의 비대칭 제어  $\alpha_1=120^\circ$ ,  $\alpha_2=150^\circ$ 의 출력전압56 그림 3.8 인버터 모드의 제어에 따른 출력전압과 전류의 고조파 분석 57

## <표 목 차>

| 丑 2.1 | 초전도 에너지저장시스템의 구간 해석04 |

|-------|-----------------------|

| 哥 2.2 | 제어각에 따른 모드            |

# A Study on the asymmetric control of 3-phase thyristor bridge for Superconducting Magnet Energy Storage (SMES)

by Seung-Hyun, Kim

Department of Electrical & Electronics Engineering

The Graduate School of Korea Maritime and Ocean University

Busan, Republic of Korea

#### **Abstract**

In this paper, in general three-phase thyristor bridge circuits are used in various fields of voltage and current control such as AC-DC converter, reversible speed adjustment of large motors, and energy storage devices. Among the various energy storage devices developed so far, superconducting energy storage devices have a relatively large energy storage capacity and high response speed, which is suitable for

a system requiring frequent charge and discharge of a long time. In the SMES three-phase thyristor bridge circuit, energy is stored in the SMES by symmetrical or asymmetrical control of the alpha angles at which thyristors are turned on, and reverse voltage is generated during regeneration period in which to regenerate energy is supplied on the power supply side. This paper describes the control characteristics of power converters for SMES

In this paper, we have studied a method to increase the power factor by minimizing reactive power by asymmetric control in a 3-phase thyristor, which is a power converter for storing energy in SMES.

KEY WORD: Superconducting Magnet Energy Storage (SMES), 3-phase thyristor bridge, Symmetrical control, Asymmetrical control

## 초전도 에너지 저장 장치용 3상 사이리스터 브리지의 비대칭 제어에 관한 연구

*김 승 현* 한국해양대학교 대학원 전기전자공학과

추록

일반적으로 3상 사이리스터 브리지 회로는 AC-DC 변환장치, 대형 모터의 가역속도 조정, 에너지 저장 장치 등 전압, 전류 제어의 여러 분야에서 사용되고 있다. 에너지 저장 장치에서는 현재까지 개발된 여러 가지 대용량에너지 저장 장치들 중 초전도 에너지 저장 장치 (Superconducting Magnet Energy Storage, SMES)는 상대적으로 에너지 저장용량이 크고 응답속도가빨라서 오랜 시간동안 잦은 충·방전이 요구되는 시스템에 적용하기에 적합하고 사이리스터 브리지를 대칭 제어하는 대신에 비대칭 제어를 하면 상대적으로 평균 출력전압은 감소하지만 유효전력을 최대화하면서 무효전력을 최소화하여 역률을 증가시킬 수 있다. 따라서 SMES용 3상 사이리스

터 브리지 회로에서 사이리스터가 점호되는  $\alpha$ 각을 대칭 또는 비대칭 제어함으로써 특징을 분석하였고 에너지를 SMES에 저장하고 회생 시에는 저장된 에너지를 입력 전원 측에 공급하게 된다.

본 논문에서는 SMES에 에너지를 저장하기 위한 전력변환기인 3상 사이리스터에서 비대칭 제어를 함으로써 무효전력을 최소화 시켜 역률을 증가시킬 수 있는 방법에 대하여 연구하였다.

KEY WORD: 초전도 에너지 저장 장치(Superconducting Magnet Energy Storage, SMES), 3상 사이리스터 브리지, 대칭 제어, 비대칭 제어

## 제 1 장 서 론

최근 화석 연료의 고갈문제와 동시에 신재생에너지의 필요성이 크게 증가하고 있다.[1] 하지만 신재생에너지는 주변 환경과 조건에 영향을 많이 받아 안정적인 전력공급이 어렵다. 따라서 생산되는 에너지의 양이 불확실한 발전기술을 계통에 연계하기 위해서 출력 안정화 기술의 중요성이 증가되었고 발전량이 계통의 수요보다 클 때, 남는 전력을 활용하여 에너지를 저장하고, 발전량이 수요보다 낮아지면 저장된 에너지를 계통에 보내주는 방식의 에너지 저장 장치가 필요하다.[2-3]

에너지저장장치에서 현재까지 개발된 여러 가지 대용량 에너지 저장 장치들 중 초전도 에너지 저장 장치(Superconducting Magnet Energy Storage, SMES)는 상대적으로 에너지 저장용량이 크고 응답속도가 빨라서 오랜 시간동안 잦은 충·방전이 요구되는 시스템에 적용하기에 적합하고 초전도 현상을 이용하면 전기저항이 제로가 되기 때문에 대용량, 대출력, 고효율의 전력기기를 다룰 수 있다.[6-10]

충방전하는 배터리의 경우 횟수의 제약이 있으며, 빈도가 잦을 경우 수명과 관계되는데 초전도 에너지 저장 장치의 경우 충방전에 의한 성능 저하가 없어서 장기간 사용이 가능하다는 장점을 가지고 있다. 이를 제어 하는 전력변환기는 사이리스터 브리지가 적합하다.[4]

일반적으로 사이리스터는 비교적 높은 전압, 전류 범위에서 사용되는 반도체 소자이고, 3상 사이리스터 브리지 회로는 AC-DC 변환장치, 대형 모터의 가역속도 조정, 에너지저장장치 등 전압, 전류 제어의 여러 분야에 서 사용되고 있다.[13-20] 하지만 위상을 제어하면서 출력 측의 평균 전압

이 감소하게 되고 전류의 파형에서 고조파 성분이 나타나게 되어서 출력 측에 추가적인 장치나 사이리스터 브릿지 회로에서 제어각(α)을 대칭 제어하지 않고 비대칭 제어를 하여 고조파를 감량시키거나 사이리스터 브리지를 직병렬로 연결시켜 이를 보완하는 방법이 연구되어 왔지만,[22-26] 사이리스터 브리지의 비대칭제어에 관한 연구는 다소 부진하다.[14, 23-24]

3상 사이리스터 브리지 회로에서 정측(Positive group)과 부측(Negative group)으로 나뉘어 제어각을 대칭 제어 하였을 경우 전압과 전류는 제어각 0°에서 90°까지는 양의 값을 가지는 컨버터 모드와 양측의 제어각 90°가 되었을 경우 출력 평균전압은 0V가 되고, 제어각 90°에서 180°까지는 음의 값을 가지는 인버터 모드로 해석하였다.[24]

사이리스터 브리지에서 무효전력을 최소로 하기 위해서 한 측의 제어 각을 최대 또는 최소로 제어하고 나머지 측을 출력에 따라 조정하게 되면 무효전력은 최소로 하고 원하는 출력을 얻을 수 있고 출력 전압을 정밀하 게 제어하여 얻어 낼 수 있다.[14]

본 논문에서 사이리스터 브리지 회로를 이용하여 SMES에 에너지를 저장하기 위한 전력변환기로써, 제어각을 0 ~ 90 로 제어하였을 시 컨버터모드로 해석하고 제어각을 90°~ 180°로 제어하였을 시 인버터모드로해석하여 비대칭 제어하고 무효전력을 최소로 하는 출력 평균전압을 SMES에 저장하고 회생 시에는 저장된 에너지를 입력 전원 측에 공급한다.

## 제 2 장 이 론

## 2.1 초전도 에너지 저장 시스템 (SMES)

초전도 에너지 저장 시스템은 초전도 성질을 갖는 금속으로 인덕터를 만들고 초전도 상태를 만들어줌으로써 저항성분이 0이 되는 환경을 만들어주어 초전도 성질의 인덕터가 에너지를 손실 없이 저장하는 시스템이다.

(a) 초전도 에너지 저장 장치 회로도

(b) 초전도 에너지 저장 장치의 시스템도

그림 2.1 초전도 에너지 저장 시스템의 에너지 저장 방법

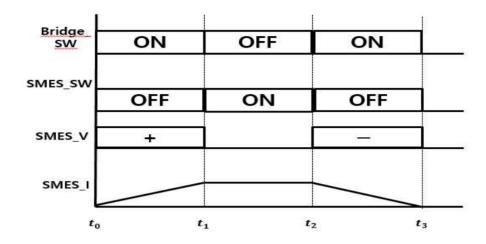

Fig. 2.1 Energy storage method of superconducting energy storage system 그림 2.1은 초전도 에너지 저장 시스템의 에너지 저장 방법에 대하여 나타내었다.

표 2.1 초전도 에너지 저장 시스템의 구간 해석

Table 2.1 Interpretation of superconducting energy storage system

| 구간          | 내 용                             |

|-------------|---------------------------------|

|             | 3상 사이리스터 전력변환기를 통하여 초전도 에너지저장   |

| $t_0 - t_1$ | 장치에 에너지를 저장                     |

| , ,         | 3상 사이리스터 전력변환기를 OFF 시키고 초전도 스위치 |

| $t_1 - t_2$ | 를 ON 시켜 초전도 에너지저장장치의 에너지를 환류    |

|             | 초전도 스위치를 OFF 시키고 3상 사이리스터 전력변환기 |

| $t_2-t_3$   | 의 스위치를 ON시켜 초전도 에너지저장장치의 에너지를   |

|             | 회생                              |

### 2.2 사이리스터 브리지 제어

3상 사이리스터 브리지 회로로써 3상 AC 220V를 사용하여 입력전원으로 사용하였으며, 사이리스터는 비교적 높은 전압, 전류 범위에서 사용되는 반도체 스위칭 소자이고 일반적으로 사이리스터 브리지 회로는 AC-DC 변환장치, 대형모터의 가역속도 조정, 에너지 저장 장치 등 여러분야에서 사용되어 왔다.[13-20]

그림 2.2에서 3상 AC 220V는 120°의 위상차를 가지는 전압으로 식 (2.1)로 나타낼 수 있다.

$$e_{a} = V_{m}\sin(wt + \frac{\pi}{2})$$

[V]

$$e_{b} = V_{m}\sin(wt - \frac{\pi}{2})$$

[V]

$$e_{c} = V_{m}\sin(wt + \frac{5\pi}{6})$$

[V]

각각의 선간전압은 식(2.2)로 나타낼 수 있다.

$$\begin{split} e_{ab} &= \sqrt{3} \ V_m \sin(wt + \frac{\pi}{3}) \\ e_{bc} &= \sqrt{3} \ V_m \sin(wt - \frac{\pi}{3}) \\ e_{ca} &= \sqrt{3} \ V_m \sin(wt + \pi) \end{split} \tag{2.2}$$

선간전압은 상전압의  $\sqrt{3}$  배이고, 위상이  $30^{\circ}$  만큼 앞선 전압이  $120^{\circ}$ 의 위상차를 두고 연속된다.[13]

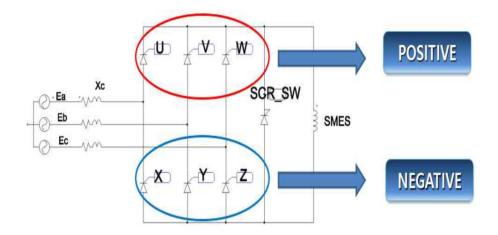

그림 2.2 3상 사이리스터 브리지 회로 제어

Fig. 2.2 3-phase thyristor bridge circuit control

사이리스터 그룹을 정측(Positive group), 부하 측에서 전류가 나가는 사이리스터 그룹을 부측(Negative group)으로 구성하여 3개의 사이리스터가하나의 그룹을 가지고 있고 정측(Positive group)의 제어각을  $\alpha_1$ , 부측 (Negative group)의 제어각을  $\alpha_2$ 로 명시하였을 때, 대칭제어는  $\alpha_1=\alpha_2$ , 비대칭제어는  $\alpha_1\neq\alpha_2$ 이다.

그림 2.3의 사이리스터 브리지 회로는 사이리스터를 정측(Positive group)과 부측(Negative group)으로 대칭 및 비대칭제어 목적으로 그룹을 나누었고, 부하 측 인덕턴스( $X_L$ )는 초전도 에너지 저장 장치로써 용량이 매우 크다고 가정하였을 때, 부하 전류  $I_d$ 는 일정하게 흐르게 될 것이라 판단된다.

#### 표 2.2 제어각에 따른 모드

Table 2.2 Mode according to control angle

|         | Converter mode                      | Inverter mode                       |

|---------|-------------------------------------|-------------------------------------|

| 제어각 범위  | $\alpha_1 + \alpha_2 < 180^{\circ}$ | $\alpha_1 + \alpha_2 > 180^{\circ}$ |

| 평균 출력전압 | (+)                                 | (-)                                 |

그룹을 나누어 정측 제어각을  $\alpha_1$ , 부측 제어각을  $\alpha_2$ 로 제어하였을 때, 표 2.2 은 컨버터 모드와 인버터 모드로 동작할 때의 제어각 범위와 평균 출력전압을 나타내었고 원하는 출력전압을 얻기 위해서 제어되어야 하는 제 어각을 나타내었다.[24]

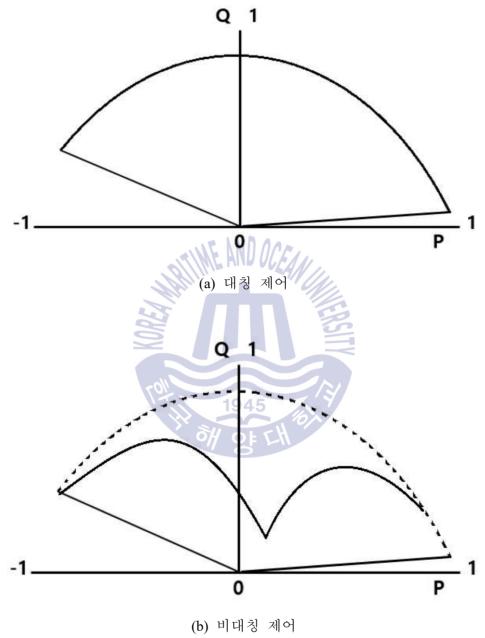

그림 2.4 은 대칭 제어와 비대칭 제어에서의 유효전력(P)와 무효전력(Q)를 나타낸 그림이고 대칭 제어에서 제어각에 따라 무효전력이 증대되는 것과 다르게 비대칭 제어에서 평균 출력전압은 감소하지만 유효전력을 최대한으로 얻고 무효전력을 최소화하는 방식으로 대칭 제어와 비교하였다.

그림 2.3 제어 방법에 따른 유효전력(P)와 무효전력(Q)의 관계

Fig. 2.3 Relationship between active power(P) and reactive power(Q) according to the control method

## 2.2.1 대칭 제어 (Symmetry control)

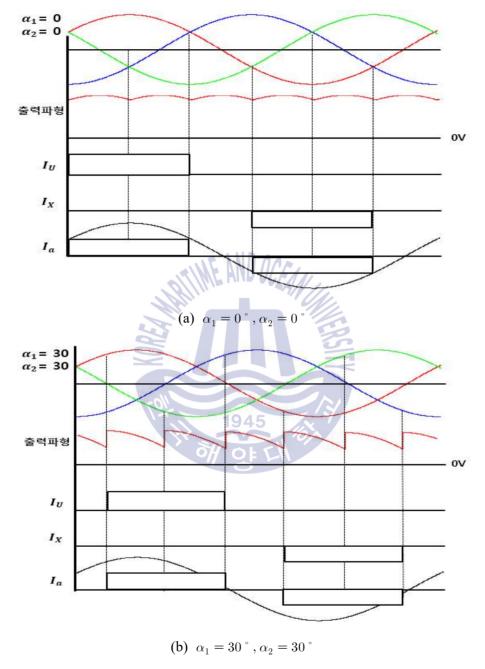

대칭제어에서는 제어각  $\alpha_1$ 과  $\alpha_2$ 를 같게 하여  $0^\circ$ 에서  $90^\circ$ 까지로 제어하였을 경우 평균 출력전압은 양의 값을 갖게 되고 제어각  $90^\circ$ 에서는 평균 출력전압은 0 [V]가 된다.  $90^\circ$ 에서  $180^\circ$ 까지는 음의 값을 갖는 평균 출력전압을 얻을 수 있고  $180^\circ$ 에 가까워질수록 (-)값이 증대된다. 그림 2.5는 제어각  $\alpha_1$ 과  $\alpha_2$ 를  $0^\circ$ 에서  $90^\circ$ 까지의 범위에서 대칭 제어를 하였을때의 결과이며 대칭 제어에서 제어각의 변화에 따라 출력파형과 a상에서 흐르는 전류  $I_a$ 는 사이리스터 U와 X에 흐르는 전류로  $I_V$ 와  $I_X$ 로 정의하고 이때의 전류는  $120^\circ$ 의 위상을 가지고 흐르게 된다.

그림 2.5(a) 는 대칭 제어에서 제어각  $\alpha_1$ 과  $\alpha_2$ 를  $0^\circ$ 로 제어하여 점호하였을 때, 출력파형과 a상에서 흐르는 사이리스터 U와 X의 전류를 나타내었고 제어각  $0^\circ$ 에서는 지연 점호를 하지 않기 때문에 다이오드의 출력파형과 같다.

그림 2.5(b) 는 제어각  $\alpha_1$ 과  $\alpha_2$ 를 30°로 제어하여 점호하였을 때의 출력 파형과 a상에서 흐르는 사이리스터 U와 X의 전류를 나타내었고 제어각 30°로 제어하였을 경우 30°만큼 지연 점호가 일어나기 때문에 출력파형과 전류는 지연되어 나타나고 평균 출력전압도 낮아지게 된다.

그림 2.5(c) 는 제어각  $\alpha_1$ 과  $\alpha_2$ 를 60°로 제어하여 점호하였을 때의 출력 파형과 a상에서 흐르는 사이리스터 U와 X의 전류를 나타내었고 제어각 60°로 제어하였을 경우 60°만큼 지연 점호가 일어나 출력파형과 전류는 지연되어 나타나고 평균 출력 전압도 0V에 가까워진다.

그림 2.4 컨버터 모드에서의 제어각 변화에 따른 대칭 제어

Fig. 2.4 Symmetrical control according to control angle in converter mode

(d)

$$\alpha_1 = 90^{\circ}$$

,  $\alpha_2 = 90^{\circ}$

그림 2.5(d) 는 제어각  $\alpha_1$ 과  $\alpha_2$ 를 90°로 제어하였을 때의 출력 파형과 a 상에서 흐르는 사이리스터 U와 X의 전류이고 제어각 90°로 제어하였을 경우 90°만큼 지연 점호가 일어나게 되고 이때의 평균 출력전압은 0V가된다. 대칭제어에서 컨버터 모드는 제어각 범위 90°에서 끝나게 되고 90°이상의 범위에서 인버터 모드로 해석한다.

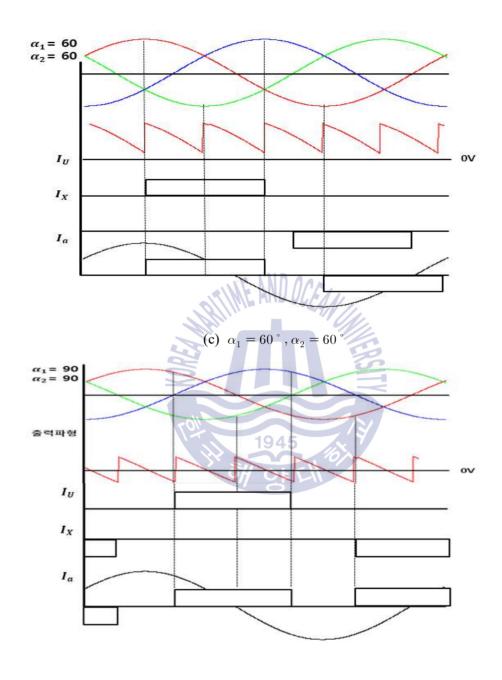

그림 2.6은 90° 이상의 범위인 인버터 모드에서의 제어각  $\alpha_1$ 과  $\alpha_2$ 를 90°에서 180°까지의 범위에서 대칭 제어를 하였을 때의 파형이며 이때의 출력파형은 음의 값을 가지게 된다. 그림 2.4에서는 인버터 모드에서의 제어각 변화에 따른 대칭 제어를 나타내었고 컨버터 모드에서 해석하였던 것과 같이 제어각의 변화에 따라 출력파형과 a상에서 흐르는 전류  $I_a$ 를 사이리스터 U와 X에 흐르는 전류로  $I_V$ 와  $I_X$ 로 정의하고 전류는 120°의 위상을 가지고 흐르게 된다.

그림 2.6(a) 는 대칭 제어에서 제어각  $\alpha_1$ 과  $\alpha_2$ 를  $120^\circ$ 로 제어하여 점호하였을 때를 나타내며 인버터 모드로 동작하게 된다. 출력파형과 a상에서 흐르는 사이리스터 U와 X의 전류를 나타내었고 인버터 모드에서는 제어 각이 커질수록 출력파형은 (-)로 커지게 된다.

그림 2.6(b) 는 대칭 제어에서 제어각  $\alpha_1$ 과  $\alpha_2$ 를  $150\,^\circ$ 로 제어하여 점호하였을 때를 나타내며 출력파형과 a상에서 흐르는 사이리스터 U와 X의 전류를 나타내었고 인버터 모드에서의 동작을 나타내고 있다.

그림 2.6(c) 는 대칭 제어에서 제어각  $\alpha_1$ 와  $\alpha_2$ 를 180°로 제어하여 점호하였을 때를 나타내며 출력파형과 a상에서 흐르는 사이리스터 U와 X의 전류를 나타내었고  $\alpha_1$ 와  $\alpha_2$ 가 0°로 제어하였을 경우의 완전히 반전되는 파형이 나타나게 된다.

그는 2.3 단시의 모드 1/기의 제기의 단위 1 에는 데 6 제기

Fig. 2.5 Symmetrical control according to control angle in inverter mode

- 14 -

## 2.2.2 비대칭 제어 (Asymmetry control)

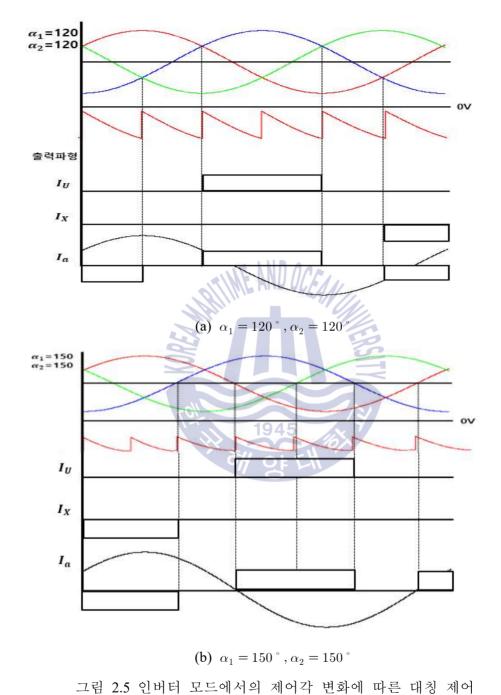

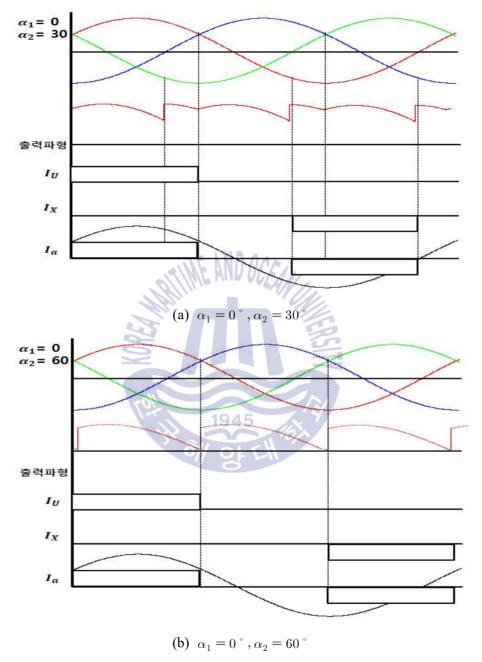

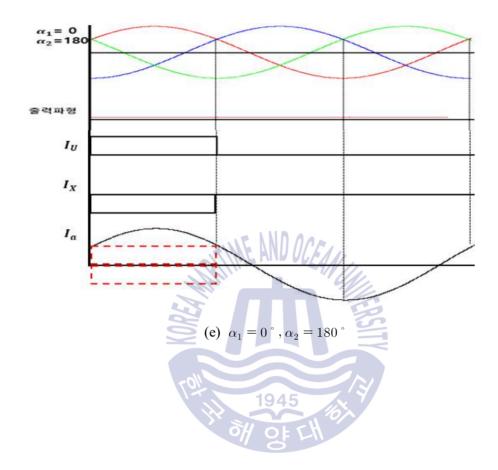

비대칭제어에서는 제어각  $\alpha_1$ 과  $\alpha_2$ 를 다르게 제어하는 것이며  $\alpha_1$ 을  $0^\circ$ 로 고정하고  $\alpha_2$ 를  $180^\circ$ 까지 점차적으로 제어하였을 경우 비대칭제어에서 컨버터 모드로 동작하게 되어 평균 출력전압은 양의 값을 갖게 되고 a상에 흐르는 전류  $I_a$ 에서  $I_U$ 와  $I_X$ 가 제어각에 따라 지연 점호되면서 무효전력을 최소화시키면서 평균 출력전압을 제어할 수 있다.

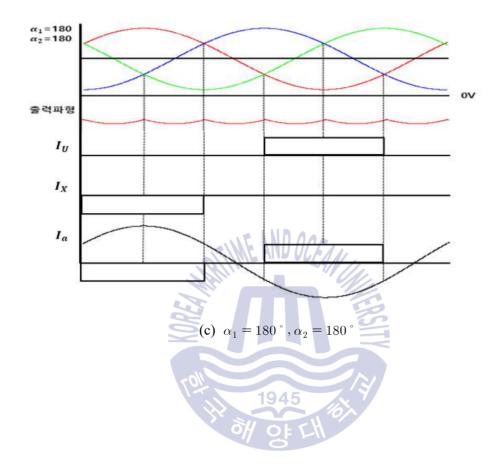

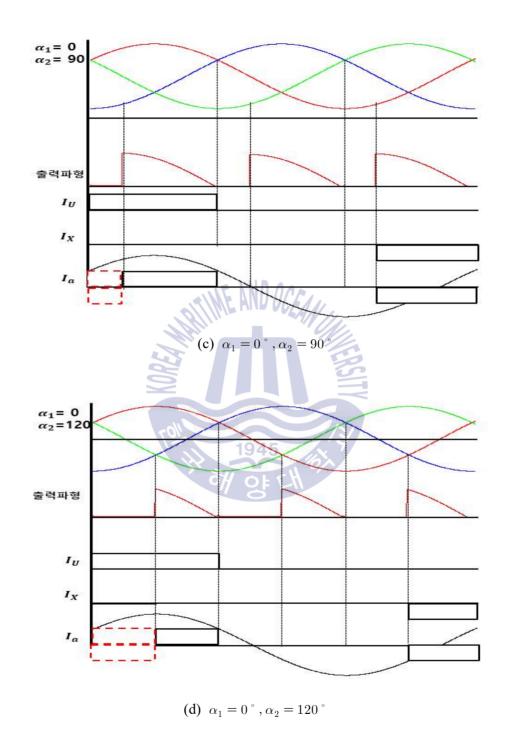

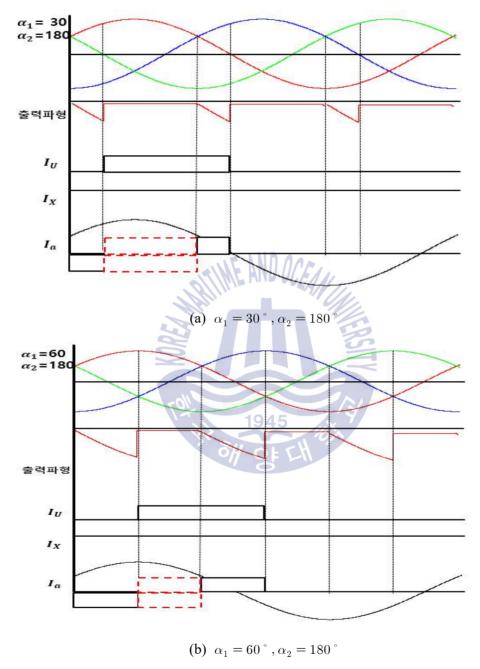

$\alpha_2$ 를  $180\,^\circ$ 로 고정시키고  $\alpha_1$ 를  $180\,^\circ$ 까지 점차적으로 제어하였을 경우비대칭제어에서 인버터 모드로 동작하게 되어 평균 출력전압은 음의 값을 갖게 되고  $\alpha$ 상에 흐르는 전류  $\alpha$ 에서  $\alpha$ 0  $\alpha$ 1  $\alpha$ 2  $\alpha$ 3 제어각에 따라 지연 점호되면서 무효전력을 최소화시키면서 평균 출력전압을 제어할 수 있다.

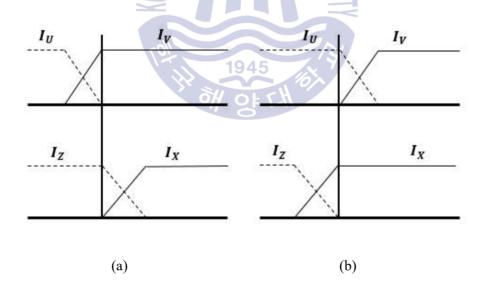

그림 2.7는 비대칭제어에서 제어각  $\alpha_1$ 을  $0^\circ$ 로 고정시키고  $\alpha_2$ 를  $180^\circ$ 로 제어각을 점차적으로 증가시켰을 경우이고 비대칭제어에서의 제어각 변화에 따라 출력파형과 a상에 흐르는  $I_a$ 는 사이리스터 U와 X에 흐르는 전류로  $I_U$ 와  $I_X$ 로 나타내었고 전류는  $120^\circ$ 의 위상을 가지고 흐르게 되지만비대칭제어를 함으로써 전류의 위상이 지연되고 서로 상쇄되는 구간이 발생하면서 평균 출력전압을 제어하면서 무효전력을 최소화 시키는 범위를가지게 된다.

그림 2.7(a)는 비대칭 제어에서 제어각  $\alpha_1$ 을 0°로  $\alpha_2$ 를 30°로 제어하여 점호하였을 때, 출력파형과 a상에서 흐르는 사이리스터 U와 X의 전류를 나타내었고  $\alpha_2$ 를 30°로 지연 점호하기 때문에 사이리스터 X의 전류  $I_X$ 는 위상이 30°만큼 지연되고 a상의 전류  $I_a$ 에서 전류가 겹치지 않는 구간으로 영향을 주지 않는다.

그림 2.6 컨버터 모드에서의 제어각 변화에 따른 비대칭제어

Fig. 2.6 Asymmetrical control according to control angle in converter mode

그림 2.7(b)는 비대칭 제어에서 제어각  $\alpha_1$ 을 0°로  $\alpha_2$ 를 60°로 제어하여 점호하였을 때, 출력파형과 a상에서 흐르는 사이리스터 U와 X의 전류를 나타내었고  $\alpha_2$ 를 60°로 지연 점호하기 때문에 사이리스터 X의 전류  $I_X$ 는 위상이 60°만큼 지연되게 되고 지연되지 않는 사이리스터 U의 전류  $I_U$ 의 관계에서 a상의 전류  $I_a$ 는 최초로 전류가 겹치는 과정을 가지게 된다.

그림 2.7(c)는 비대칭 제어에서 제어각  $\alpha_1$ 을  $0^\circ$ 로  $\alpha_2$ 를  $90^\circ$ 로 제어하여 점호하였을 때, 출력파형과 a상에서 흐르는 사이리스터 U와 X의 전류를 나타내었고  $\alpha_2$ 를  $90^\circ$ 로 지연 점호하기 때문에 사이리스터 X의 전류  $I_X$ 는 위상이  $90^\circ$ 만큼 지연되게 되고 지연되지 않는 사이리스터 U의 전류  $I_U$ 의 관계에서 a상의 전류  $I_a$ 는 전류가  $I_X$ 의 영향으로  $30^\circ$ 의 위상 범위만큼 서로 상쇄되어 없어지는 구간을 갖게 되고 무효전력을 최소화하면서 평균 출력전압을 제어할 수 있는 파형을 나타내었다.

그림 2.7(d)는 비대칭 제어에서 제어각  $\alpha_1$ 을 0°로  $\alpha_2$ 를 120°로 제어하여 점호하였을 때, 출력파형과 a상에서 흐르는 사이리스터 U와 X의 전류를 나타내었고  $\alpha_2$ 를 120°로 지연 점호하기 때문에 사이리스터 X의 전류  $I_X$ 는 위상이 120°만큼 지연되게 되고 지연되지 않는 사이리스터 U의 전류  $I_U$ 의 관계에서 a상의 전류  $I_a$ 는 전류가  $I_X$ 의 영향으로 60°의 위상 범위만큼 서로 상쇄되어 없어지는 구간을 갖게 되고 무효전력을 최소화하면서 평균 출력전압을 제어할 수 있게 된다.

그림 2.7(e)는 비대칭 제어에서 제어각  $\alpha_1$ 을 0°로  $\alpha_2$ 를 180°로 제어하여 점호하였을 때, 출력파형과 a상에서 흐르는 사이리스터 U와 X의 전류를 나타내었고  $\alpha_2$ 를 180°만큼 지연 점호하면 사이리스터 X의 전류  $I_X$ 는 사이리스터 U의 전류  $I_U$ 와 완전히 겹쳐 서로 상쇄되는 파형을 나타내었고 그 결과 평균 출력전압은 0V가 된다.

그림 2.7 인버터 모드에서의 제어각 변화에 따른 비대칭제어

Fig. 2.7 Asymmetrical control according to control angle in inverter mode

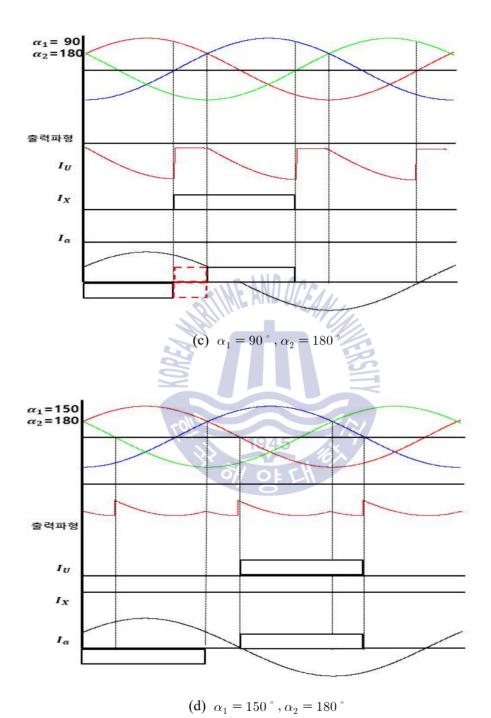

그림 2.8 는 인버터 모드에서의 제어각 변화에 따른 비대칭제어를 하였을 때의 경우이며, 제어각  $\alpha_2$ 를  $180^\circ$ 로 고정 제어하고  $\alpha_1$ 를 점차적으로 증가시켜 점호하였을 때의 출력파형과 a상에서 흐르는 사이리스터 U와 X의 전류를 나타내었고  $\alpha_2$ 는  $180^\circ$ 로 지연 점호하고  $\alpha_1$ 은 점차적으로 증가되어 지연 점호되기 때문에 사이리스터 X의 전류  $I_X$ 는 위상이  $180^\circ$ 만큼 지연되게 되고  $\alpha_1$ 의 영향으로 제어되는 사이리스터 U의 전류  $I_U$ 의 관계에서 a상의 전류  $I_a$ 는 인버터 모드에서  $\alpha_1$ 의 영향으로 서로 겹쳐 상쇄되어 지거나 겹치지 않는 구간을 가지게 된다.

그림 2.8(a)에서  $\alpha_2$ 를  $180\,^\circ$ 로 고정시키고  $\alpha_1$ 을  $30\,^\circ$ 로 제어하였을 때, 인 버터 모드로 동작하게 되고 출력파형과 a상에서 흐르는 사이리스터 U와 X의 전류를 나타내었고  $\alpha_1$ 과  $\alpha_2$ 의 제어에 의한 지연 점호에서 전류는 서로 겹쳐 상쇄되어 평균 출력전압을 작게 얻고 무효전력을 최소화 하였다.

그림 2.8(b)에서  $\alpha_2$ 를 180°로 고정시키고  $\alpha_1$ 을 60°로 제어하였을 때, 인 버터 모드로 동작되고 출력파형과 a상에서 흐르는 사이리스터 U와 X의 전류를 나타내었고  $\alpha_1$ 가 60°로 제어하였을 경우  $\alpha_1$ 을 30°로 제어하였을 때보다 상쇄되는 구간이 적어지기 때문에 평균 출력전압은 증가한다.

그림 2.8(c)에서  $\alpha_2$ 를 180°로 고정시키고  $\alpha_1$ 을 90°로 제어하였을 때의 출력파형과 a상에서 흐르는 사이리스터 U와 X의 전류를 나타내었고  $\alpha_1$ 가 90°로 제어하였을 경우  $\alpha_1$ 을 30°와 60°로 제어하였을 때보다 상쇄되는 구간이 적어지기 때문에 평균 출력전압은 증가하게 된다.

그림 2.8(d)에서  $\alpha_2$ 를 180°로 고정시키고  $\alpha_1$ 을 150°로 제어하였을 때의 출력파형과 a상에서 흐르는 사이리스터 U와 X의 전류를 나타내었고 겹치는 구간이 존재하지 않고 인버터 모드에서 동작하게 된다.

### 2.3 제어에 따른 출력전압 및 출력전류

제어각  $\alpha$ 각에 의한 전압과 전류는 부하의 종류와 크기에 따라 달라진다. 점호 제어각  $\alpha_1$ 과  $\alpha_2$ 가  $\alpha_1+\alpha_2<180$ °인 경우 (+)로 출력 평균전압이 나타나고,  $\alpha_1+\alpha_2>180$ °인 경우 (-)로 출력 평균전압이 나타나게 된다. 출력전압  $V_{\alpha}$ 를 퓨리에 급수로 전개하면 식 (2.3)과 같다.[12-15]

$$V_o = V_d + \sum \sqrt{A_n^2 + B_n^2} \cos(n\omega t - \theta_n)$$

[V]

출력 평균전압의 직류성분( $V_d$ ) 은 식 (2.4)와 같다.

$$V_{d} = \frac{3}{2\pi} [\int_{\alpha_{1}+\pi/3}^{\alpha_{2}+2\pi/3} \sqrt{3} \; V_{m} \sin(\omega t + \frac{\pi}{3}) d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{1}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{1}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{1}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{1}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{1}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{1}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{1}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{1}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{1}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{1}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{1}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+2\pi/3}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t + \int_{\alpha_{2}+\pi}^{\alpha_{2}+\pi} \sqrt{3} \; V_{m} \sin\omega t \, d\omega t$$

$$V_{d} = \frac{3\sqrt{3}}{2\pi} V_{m} (\cos\alpha_{1} + \cos\alpha_{2})$$

[V] (2.4)

실효값( $V_R$ )은 식 (2.5)와 같다.

$$V_R = \, [rac{3\pi}{2} \int_{lpha_1 + \, \pi/3}^{lpha_2 + \, 2\pi/3} e_{ab}^{\,\,\,\,2} \, d\omega t + \, \int_{lpha_2 + \, 2\pi/3}^{lpha_1 + \,\,\pi} e_{ac}^{\,\,\,\,2} \, d\omega t]^{1/2}$$

$$V_R = \sqrt{3} V_m \left[ \frac{1}{2} + \frac{3\sqrt{3}}{8\pi} (\cos 2\alpha_1 + \cos 2\alpha_2) \right]^{1/2} \quad [V]$$

(2.5)

출력전류(I<sub>0</sub>)는 식 (2.6)와 같다.

$$I_{o} = I_{d} + \sum \frac{\sqrt{A_{n}^{2} + B_{n}^{2}}}{[R^{2} + (n\omega L)^{2}]^{1/2}} \cos(n\omega t - \theta_{n} - \phi_{n})$$

[A] (2.6)

$$(\phi_n = \tan^{-1}(\frac{n\omega L}{R}))$$

평균 출력전류의 직류성분 $(I_d)$ 는 평균 출력전압 $(V_d)$ 와 유도기전력 $(V_C)$ 를 고려하였을 때,

$$I_d = \frac{V_d - V_C}{R} \tag{2.7}$$

식 (2.7) 으로 나타낼 수 있으며 식 (2.4)에 대입하면, 1945

$$I_{d} = \frac{\sqrt{3} V_{m}}{R} \left[ \frac{3}{2\pi} (\cos \alpha_{1} + \cos \alpha_{2}) - V_{C} \right]$$

[A]

식 (2.8)로 나타낼 수 있다.

부하에 걸리는 고조파성분의 값은 식 (2.9)로 나타낼 수 있고 고조파성 분의 실효값은 식 (2.10)으로 나타내면

$$I_{nR} = \frac{C_n}{\sqrt{2}} \tag{2.9}$$

$$I_{Ro} = \sqrt{\sum I_{nR}^2}$$

[A]

(

$$C_n = \frac{\sqrt{{A_n}^2 + {B_n}^2}}{[R^2 + (n\omega L)^2]^{1/2}}$$

)

식 (2.9)와 식 (2.10)으로 유효 전류의 실효값  $I_R$ 은 나타내면 식 (2.11)과 같다.

$$I_R = \sqrt{I_d^2 + I_{Ro}^2}$$

[A]

## 2.4 사이리스터 브리지의 비대칭 제어 동작 특성

대칭 제어를 할 경우에는 각 상에 흐르는 전류  $i_a$ ,  $i_b$ ,  $i_c$ 는  $60\,^\circ$ 의 위상 차를 가지고  $120\,^\circ$ 만큼 흐르게 되지만, 비대칭 제어에서는 대칭 제어와 달리 제어각  $\alpha_1$ 과  $\alpha_2$ 에 따라 위상이 달라지기 때문에 그에 의한 출력 평 균전압의 강하와 전환각(u)을 고려하여야 한다.

그림 2.8 3상 사이리스터 브리지의 전환 구간

Fig. 2.8 Switching section of 3-phase thyristor bridge

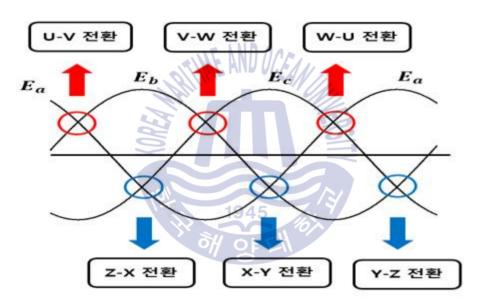

그림 2.9은 3상 사이리스터 브리지는 총 6번의 전환이 이루어지는 구간을 그림으로 나타내었으며, 전환되는 지점에서 제어각의 제어에 따라지연 점호가 이루어진다.

# 2.4.1 전류의 겹침과 전환각(u)

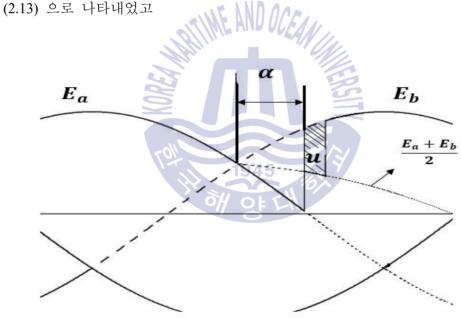

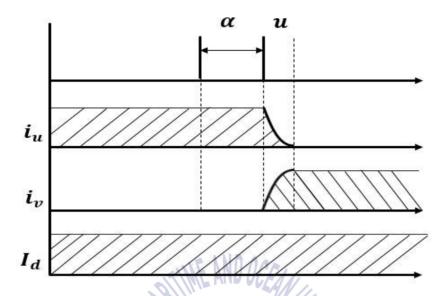

사이리스터 브리지의 동작 특성을 분석하기 위해서는 입력리액턴스 $(X_C)$ 의 영향과 각각의 사이리스터가 턴-오프될 때, 전환각(u)를 고려하여야 한다. 그림 2.10는 사이리스터 U와 Z가 도통되어 흐르고 있는 상태에서 사이리스터 V가 도통되었을 때, 전환각(u) 동안 전압은  $(e_a+e_b)$  / 2 로 떨어지게 되며 전류는 그림 2.11과 같이 입력 리액턴스의 영향을 받아 U에서 V로 전환될 때의 각 상의 전압을 폐루프 방정식으로 표현한 식이 (2.12), 전류는

그림 2.9 사이리스터 U-V 전환 시 제어각 $(\alpha)$ 와 전환각(u)

Fig. 2.9 The control angle  $(\alpha)$  and the switching angle (u) when the conducting of the thyristor of the 3-phase bridge is transferred from U-Z to U-V

그림 2.10 사이리스터 U-V 전환 시 전류  $i_u$ ,  $i_v$ 와 평균 출력전류  $I_d$ Fig. 2.10 Current  $i_u$ ,  $i_v$  and average output current  $I_d$  when the conducting of the thyristor of the 3-phase bridge is transferred from U-Z to U-V

그림 2.11에서 사이리스터 U-V가 전환이 이루어질 때,  $\alpha$ 만큼의 지연점 호가 일어나고 전류가 전환각 u동안 전환하는 기간을 가지게 된다.[15, 30]

$$e_a - X_C \frac{di_a}{dt} + X_C \frac{di_b}{dt} - e_b = 0 {(2.12)}$$

$$i_a + i_b = i_d \tag{2.13}$$

사이리스터 U에서 V로 전환될 때,

$$i_a = i_d - \frac{\sqrt{3} V_m}{2X_c} [\cos \alpha_1 - \cos(\omega t + \alpha_1)]$$

[A]

$$i_b = \frac{\sqrt{3} V_m}{2X_c} [\cos \alpha_1 - \cos(u + \alpha_1)]$$

[A]

각 상의 출력전류는 식 (2.14)와 (2.15)와 같고 출력 평균전압 $(i_d)$ 는  $i_a$ 에서  $i_b$ 로 전환될 때, 전환각(u)는 식 (2.16)으로 나타낼 수 있다.

$$u = \cos^{-1}\left[\cos\alpha - 2X_{cpu}\frac{i_d}{i_{dn}}\right] - \alpha$$

$$(X_{cpu} = \frac{X_c}{\sqrt{3}V_{cpu}}i_{dn})$$

(2.16)

전환각(u)는  $X_C$ 와  $i_d$ 가 커지면 전환각(u)도 길어지게 되고, 비대칭 제어를 하였을 시, 전환각  $u_1$ 과  $u_2$ 는 식 (2.17)과 (2.18)로 나타낼 수 있다.

$$u_1 = \cos^{-1}[\cos\alpha_1 - 2X_{cpu}\frac{i_d}{i_{dn}}] - \alpha_1$$

(2.17)

$$u_2 = \cos^{-1} \left[\cos \alpha_2 - 2X_{cpu} \frac{i_d}{i_{dp}}\right] - \alpha_2 \tag{2.18}$$

## 2.4.2 동시 전환과 전환 실패

비대칭 제어에서 제어각  $\alpha_1$ 과  $\alpha_2$ 가 60°의 위상차로 제어되는 경우 식 (2.19)로 나타내었을 때

$$|\alpha_1 - \alpha_2| = 60^{\circ} \tag{2.19}$$

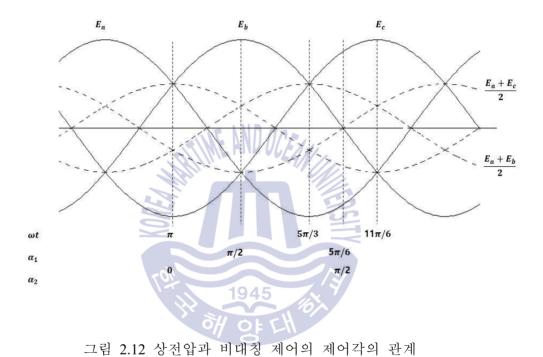

$lpha_1=lpha_2+60\,^\circlpha_1=lpha_2-60\,^\circ$ 로 관계가 성립하고 제어각  $lpha_1$ 과  $lpha_2$ 에 따라 그림 2.12로 나타낼 수 있다. 그림 2.12(a)는 사이리스터 U-V의 전환이 먼저 이루어지는 것이고 (b)는 사이리스터 Z-X의 전환이 먼저 이루어지는 것이다.

그림 2.11 3상 사이리스터의 동시 전환

Fig. 2.11 Simultaneous switching of 3-phase thyristor

동시 전환이 이루어지는 구간은 식 (2.20)과 같다.

$$\alpha_2 - u_1 < \alpha_1 - \frac{\pi}{3} < \alpha_2 + u_2 \tag{2.20}$$

Fig. 2.12 Relationships between phase voltage and asymmetrical firing angle

$\alpha_1, \ \alpha_2$

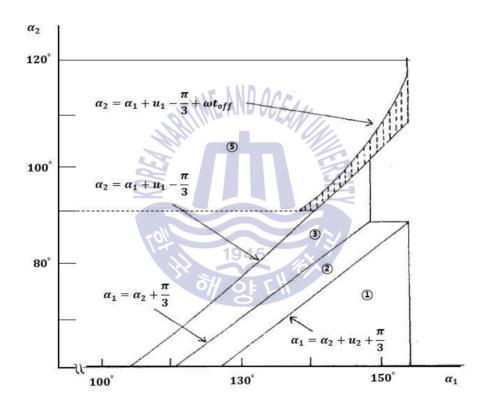

식 (2.20)에서 사이리스터 U-V가 전환 중에 Z-X가 동시 전환이 가능한 구간은 a상과 b상의 평균 전위보다 c상의 전위가 높을 때이고, 그림 2.13에서  $\alpha_1$ 이 90°가 되는 시점부터 가능하다. 90°가 되는 전에 점호 신호가들어가도 c상의 전위가 낮아 동시 전환은 불가능하다.  $\alpha_1$ 이 150°가 넘어서는 구간에서는 사이리스터 U-V가 전환된 후 Z-X의 전환이 일어나면 소자된 사이리스터가 다시 도통되어 동시 전환이 이루어지는 구간이 존재하고 그림 2.13에서 U-V로 전환된 후 Z-X의 전환이 이루어지면 a상과 c상의 평균 전위보다 b상의 전위가 높기 때문에 소자된 U가 다시 도통되고 Z-X의 전환이 끝난 후 U-V전환이 다시 이루어진다.

$$\alpha_2 \ge \frac{\pi}{2}, (\alpha_1 - u_1 - \frac{\pi}{3} \le \alpha_2 \le \alpha_1 + u_1 - \frac{\pi}{3} + \omega t_{off})$$

(2.21)

식 (2.21)은 제어각  $\alpha_1$ 과  $\alpha_2$ 에 따라 전환 상호영향이 일어나는 구간을 나타내었으며 그림 2.14로 나타내었다.

- $\alpha_2 < \frac{\pi}{2}$ , Z-X의 전환이 끝나고 U-V가 전환하는 구간

- $\alpha_2 < \frac{\pi}{2}$ , Z-X의 전환 중 U-V가 전환하는 구간

- $\alpha_2 < \frac{\pi}{2}$ , U-V 전환 중 Z-X가 전환하는 구간

- $\alpha_2 < \frac{\pi}{2}$ , U-V 전환이 끝나고 Z-X가 전환하는 구간

- $\alpha_2 > \frac{\pi}{2}$ , U-V의 전환이 끝나고 사이리스터 턴-오프 기간 내 Z-X의 전환이 시작되면서 다시 동시에 전환이 일어나는 구간

비대칭 제어에서의 가장 큰 문제점은 동시전환 중 전환 실패가 일어나는 것이다. 위의 범위를 벗어나는 구간에서는 전환 실패가 일어나는 구간이며,  $\alpha_1 > 150^\circ$ ,  $\alpha_2 > 90^\circ$  구간에서 동시전환 중 전환각(u)가 작을 경우전환 실패가 가능성이 높다.

그림 2.13 비대칭 제어에서의 전환 상호영향 구간

Fig. 2.13 Transition mutual influence section in asymmetric control

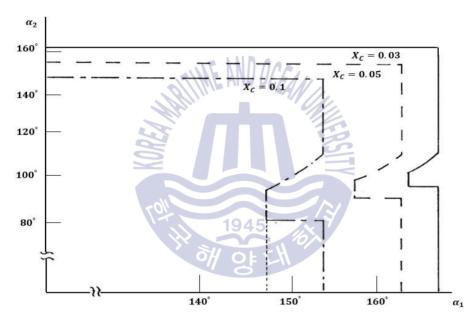

동시 전환 구간에서 전환 실패 가능성이 있는 것은 한쪽 제어각의 최대구간에서 전환각(u)가 작을 때이고, 전환각(u)는  $X_{cpu}$ 와  $i_d$ 의 크기에 따라 달라지므로  $\frac{i_d}{i_{dn}} = 1$ 이라고 가정하고 입력 리액턴스  $X_{cpu}$ 에 따른 전환실패 구간을 나타내는 것이 그림 2.15 이다.

그림 2.14 입력 리액턴스 $(X_c)$ 의 크기와 전환성공 영역

Fig. 2.14 Range of input reactance and conversion success area

그림 2.16와 그림 2.17은 그림 2.14의 동시 전환 실패 구간에 따라서 동시 전환 중 사이리스터에 흐르는 전류를 나타낸 그림이다. 그림 2.16는  $t_0-t_1$ 구간에서 U-V 전환은 끝났지만 사이리스터 턴-오프 기간에 있고  $t_1-t_2$ 구간에서 Z-X 전환이 완료되는 구간에서 전환 완료된 사이리스터 U-V의 V전류가 감소하고 소자되었던 U가 다시 도통하는 구간이고  $t_2-t_3$ 에서 다시 U-V 전환이 이루어지게 된다. 하지만  $t_3 \geq \pi$  가 되면 전환 실패가 발생한다.

그림 2.15 사이리스터 U-V의 전환 완료와 Z-X의 전환 시 전류 파형

Fig. 2.15 The current waveform when the switching of the thyristor U-V is completed and the Z-X is switched

그림 2.16 사이리스터 U-V의 전환 중 Z-X의 전환 시 전류 파형 Fig. 2.16 Current waveform when switching Z-X during switching of thyristor U-V

그림 2.17는 사이리스터 U-V 전황 중 Z-X의 전환이 일어나는 경우 U-V의 전환이 잠시 중단되고 Z-X의 전환이 이루어지는 그림이다.

그림 2.17는  $t_0-t_1$ 구간에서 U-V 전환이 이루어지던 중  $t_1-t_2$ 구간에서 Z-X 전환이 시작되고 사이리스터 U-V의 전환이 중단된다. 이 과정에서 V의 전류  $I_V$ 가 감소하고 줄어들던 U의 전류  $I_V$ 는 원상태로 돌아오고 a상의 사이리스터 U와 X가 도통되면서 순환 과정을 갖게 된다.  $t_2-t_3$ 에서 중단되었던 U-V 전환이 이루어지게 된다. 하지만  $t_3 \geq \pi$  가 되면 전환 실패가 발생한다.

그림 2.18은 사이리스터 U-V의 전환 중 Z-X의 전환이 이루어질 때 사이리스터 전체의 전류 파형을 나타낸 그림이다.

그림 2.17 사이리스터 U-V의 전환 중 Z-X의 전환 시 전체 전류 파형 Fig. 2.17 Total thyristor current waveform when switching Z-X during

thyristor U-V conversion

그림 2.18 동시 전환 과정 $(t_0-t_1)$  회로도와 전체 전류 파형

Fig. 2.18 Simultaneous thyristor switching process $(t_0-t_1)$  schematic and overall thyristor current waveform

Fig. 2.19 Simultaneous thyristor switching process $(t_1-t_2)$  schematic and overall thyristor current waveform

Fig. 2.20 Simultaneous thyristor switching process $(t_2 - t_3)$  schematic and overall thyristor current waveform

그림 2.19는 사이리스터 U와 Z로 도통되었다가 사이리스터 U-V 전환이 이루어지던 중 그림 2.20(a)에서 U-V 전환 중 Z-X의 전환이 발생하여동시 전환이 이루어지고 특히, 전환 한계점  $\alpha_1 = 150^\circ$ ,  $\alpha_2 = 90^\circ$ 에서 a, c상의 평균 전위가 b상의 전위보다 높기 때문에 U-V의 전환은 중단되고 Z-X의 전환이 완료되면 그림 2.20(b)와 같이 순환과정을 거치거나 그림 2.21(a)와 같이 중단되었던 U-V 전환이 다시 일어나고 그림 2.21(b)와 같이 사이리스터 U-V, Z-X 전환 과정이 끝나게 되고 각 상의 전류 파형은그림 2.22과 같다.

그림 2.21 사이리스터 동시 전환에서 각 상의 전류 파형

Fig. 2.21 Current waveform of each phase in simultaneous thyristor switching

1) U-V 전환 간격  $(\alpha_1+120\degree < wt < \alpha_2+180\degree)$  그림 2.18 에서  $t_0-t_1$ 은 U-V 전환 구간이며 등가 방정식으로 나타내면

$$e_b - e_a = L_c \frac{di_b}{dt} - L_c \frac{di_a}{dt} = -2L_c \frac{di_a}{dt}$$

$$(2.22)$$

식 (2.22)로 나타낼 수 있으며, 전류는  $i_d=i_a+i_b$ 로 일정하고  $\omega t=\alpha_1+120\,^\circ$ 일 때,  $i_a$ 와  $i_b$ 는

$$i_{a} = i_{d} - \frac{\sqrt{3} V_{m}}{\sqrt{2} \omega L} \left[\cos \alpha_{1} - \cos(\omega t - \frac{2\pi}{3})\right]$$

[A] (2.23)

$$i_{a} = \frac{\sqrt{3} V_{m}}{\sqrt{2} \omega L} \left[\cos \alpha_{1} - \cos(\omega t - \frac{2\pi}{3})\right]$$

[A]

2) 동시 전환 간격  $(\alpha_2 + 180 \degree < \omega t < \alpha_1 + u_1 + 120 \degree)$

그림 2.18 에서  $t_1-t_2$ 에서 동시 전환 구간이며 등가방정식으로 나타내면

$$i_a + i_b + i_c = 0 (2.25)$$

$$e_b - e_a = L_c \frac{di_b}{dt} - L_c \frac{di_a}{dt} \tag{2.26}$$

$$e_a - e_c = L_c \frac{di_a}{dt} - L_c \frac{di_c}{dt} \tag{2.27}$$

동시 전환 중 각 상의 전류는 다음과 같이 나타낼 수 있다.

$$\begin{split} i_{a} &= \frac{V_{m}}{\omega L c} [\cos(wt - \frac{5\pi}{6}) - \cos(\alpha_{2} + \frac{\pi}{6}) \\ &+ \frac{\sqrt{3} V_{m}}{2\omega L_{c}} [\cos(\alpha_{2} + \frac{\pi}{3}) - \cos\alpha_{1}] + i_{d} \end{split} \tag{2.28}$$

$$i_b = -\frac{V_m}{\omega L_c} \left[\sin \omega t - \sin (\alpha_2 + \pi)\right]$$

$$-\frac{\sqrt{3} V_m}{2\omega L_c} \left[\cos (\alpha_2 + \frac{\pi}{3}) - \cos \alpha_1\right]$$

(2.29)

$$i_c = \frac{V_m}{\omega L_c} \left[ \sin(wt + \frac{\pi}{3}) - \sin(\alpha_2 + \frac{4\pi}{3}) \right] - i_d$$

(2.30)

동시 전환구간은  $\omega t = \alpha_2 + \pi$  에서 식 (2.23), (2.34)에서  $i_a, i_b$ 를 구하고  $i_c = -i_d$ 로 대입하면 구할 수 있다.

3) 최종 동시전환 간격  $(\omega t > \alpha_2 + \pi + u_2)$

Z-X 전환 중 U-V가 최종으로 전환할 경우  $t_2$ 에서  $i_c=0$ 가 되고, 이때에  $i_a$ 의 값이  $i_{a2}$ 라고 하면 전류  $i_a$ ,  $i_b$ 에 대한 식은 식 (2.31)과 (2.32)와 같다.

$$i_{a} = \frac{\sqrt{3} V_{m}}{2\omega L} \left[\cos(\omega t - \frac{2\pi}{3}) - \cos(\alpha_{2} - \frac{2\pi}{3})\right] + i_{a2}$$

(2.31)

$$i_b = i_d - i_a \tag{2.32}$$

## 2.5 역률 및 고조파

제어각  $\alpha=0$ °로 제어하여 전환할 때에 전압의 손실을 무시한 이론적인 최대출력전압 $(V_{dm})$ 은 식 (2.34)과 같고

$$V_{dm} = \frac{3\sqrt{3}}{\pi} V_m \tag{2.34}$$

정측(Positive group) 제어각  $\alpha_1$ 과 부측(Negative group) 제어각 $\alpha_2$ 에 따른 출력전압은 식 (2.35)와 같다.

$$V_d = \frac{V_{dm}}{2} (\cos \alpha_1 + \cos \alpha_2) \tag{2.35}$$

제어각  $\alpha_1$ 과  $\alpha_2$ 에 따른 Unit output voltage ( $V_{dpu}$ )는 식 (2.36)과 같고

$$V_{dpu} = \frac{V_d}{V_{dm}} = \frac{\cos\alpha_1 + \cos\alpha_2}{2} \tag{2.36}$$

$V_{dpu}$ 와 전류  $i_d$  에 따른 유효전력과 무효전력의 관계를 Unit Active Power 와 Unit Reactive Power를 제어각  $\alpha_1$ 과  $\alpha_2$ 의 관계를 P와 Q로 나타내면

$$P = \frac{\cos\alpha_1 + \cos\alpha_2}{2} \tag{2.37}$$

$$Q = \frac{\sin\alpha_1 + \sin\alpha_2}{2} \tag{2.38}$$

식 (2.37)과 (2.38)로 나타낼 수 있고, 피상 전력  $P_a$ 는 다음과 같이 나타낸다.

$$P_{a} = \sqrt{(P^{2} + Q^{2})}$$

$$= \left[\frac{1 + \cos(\alpha_{1} - \alpha_{2})}{2}\right]^{1/2} = \cos(\frac{\alpha_{1} - \alpha_{2}}{2})$$

(2.39)

제어각  $\alpha_1$ 과  $\alpha_2$ 에서 역률 (Power factor)는 식 (2.40)과 같다.

$$\cos\phi = \frac{P}{P_a} = \cos\left(\frac{\alpha_1 + \alpha_2}{2}\right) \tag{2.40}$$

Unit output voltage ( $V_{dpu}$ )에 따라서 비대칭제어를 하였을 경우 정측(Positive group)과 부측(Negative group)으로 나뉘어 제어하는 경우에서 부측(Negative group)을 고정하고 정측(Positive group)을 제어하면 식 (2.41)과 같고 정측 (Positive group)을 고정하고 부측(Negative group)을 제어하면 식 (2.42)로 식을 나타낼 수 있다.

$$\alpha_1 = \cos^{-1}(2V_{dpu} - \cos\alpha_2) \tag{2.41}$$

$$\alpha_2 = \cos^{-1}(2V_{dpu} - \cos\alpha_1) \tag{2.42}$$

사이리스터 브리지에서 전환이 이루어질 때, 전환각(u)는 유효전력을 감소

시키고 무효전력을 증가시키게 된다. 전환각(u)에서 손실 되는 크기  $V_{cpu}$ 를 정규화한 전압강하 크기는 다음과 같다.

$$V_{dpu} = \cos\alpha - V_{cpu} = \frac{\cos\alpha + \cos(\alpha + u)}{2}$$

(2.43)

$$u = \cos^{-1}(\cos\alpha - 2V_{cpu}) - \alpha \tag{2.44}$$

비대칭 제어에서 전환각  $u_1$ 과  $u_2$ 는 다음과 같다.

$$u_1 = \cos^{-1}(\cos\alpha_1 - 2V_{cpu}) - \alpha_1 \tag{2.45}$$

$$u_2 = \cos^{-1}(\cos\alpha_2 - 2V_{cpu}) - \alpha_2 \tag{2.46}$$

사이리스터 브리지 회로에서 비대칭 제어를 하게 되면 제어각( $\alpha$ )가 역률에서  $\cos \alpha$  값이 되기 때문에 역률은 나빠지게 된다. 전력을 전압과 전류의 곱으로 나타내고 한쪽의 제어각을 최대(또는 최소)로 두고 다른 한쪽을 비대칭 제어 할 경우, 대칭 제어할 경우 전류가 전압보다 제어각 만큼 지연되어 무효전력이 많이 흐르고, 비대칭 제어할 경우 한쪽의 제어각을  $0^\circ$ 로 고정시켰을 때,  $\alpha_1 > \alpha_2 + 60^\circ$ 보다 크면 사이리스터는 순환하는 과정을 거치게 되고 입력 전류가 흐르지 않기 때문에 무효전력이 감소하게 되고 역률은 향상될 것이다.

# 제 3 장 초전도 에너지 저장 장치용 전력변환기

#### 3.1 초전도 에너지 저장 장치용 전력변환기

본 논문에서는 초전도 에너지 저장 장치에 비교적 높은 전압, 전류 범위를 가지는 사이리스터를 정측 (Positive group) 과 부측 (Negative group) 으로 나누어 비대칭 제어할 수 있는 사이리스터 브리지 회로를 전력변환기로 제안하였다. 전기저항이 제로가 되는 초전도 현상을 이용하여 전기에너지를 자기 에너지의 형태로 저장시키는 초전도 에너지 저장 장치에 에너지를 저장시키는데 목적을 두고 있고, 전기에너지를 전달하는 전력변환기를 사이리스터 브리지 회로로 구성하여 각각의 사이리스터를 정측과 부측으로 나눈 제어각을 가지고 모드별로 시뮬레이션을 하였다.[5] 필요에 따라 비대칭으로 제어하여 무효전력을 감소시키고 역률을 향상 시키는데 목적을 가지고 있고 비대칭 제어를 할때에 유의해야 할 문제점과 초전도 현상에서의 실험을 Psim 시뮬레이션을 통하여 실험을 진행하였다.

# 3.2 회로 구성

그림 3.1 초전도 에너지 저장 장치용 3상 사이리스터 브리지 회로 Fig. 3.1 3-phase thyristor bridge circuit

그림 3.1은 사이리스터 6개를 사용하여 브리지 회로를 구성하여 정측 (Positive group) 과 부측 (Negative group) 으로 나뉘어 이론적으로 검토한 대칭

제어와 비대칭 제어를 실험을 통하여 검증하는 것이 실험 목적이다.

실험을 통하여 대칭 제어와 비대칭 제어로 제어하였을 때, 전압과 전류의 파형을 검토하고 비대칭 제어로 점호하였을 경우 전환이 겹치게 되면서 순환 과정을 거치게 되고 무효전력이 감소하는 것을 시뮬레이션으로 검증하고자 한 다.

그림 3.1에서 영점 검출기 (Zero crossing point detector) 는 선간전압의 영점을 찾아 각각의 사이리스터가 전환하는 포인트 6개를 검출한다. 제안하는 시스템에서 다음 단계인 알파 제어기 (Alpha controller) 로 이행하기 전 단계로 각상의 전압 R, S, T에서 R-T, S-R, T-S 단계로 검출을 하고 (+)영역에서는 차례대로 U-V, V-W, W-U로 검출을 하게 되고 (-)영역에서는 T-S, R-T, S-R을 검출하게 되고, 검출된 포인트는 60°의 간격을 가지게 된다. 사이리스터에서 제어각을 모두 0°으로 제어하는 경우 다이오드와 같은 출력 전압을 얻을 수 있고, 상대적으로 높은 전압과 전류 범위를 취급하는 사이리스터는 Gate가 존재하기때문에 수동 소자인 다이오드와 큰 차이점을 가지게 된다.

그림 3.1에서 알파 제어기 (Alpha controller) 는 영점 검출기 (Zero crossing point detector) 에서 검출한 6개의 포인트를 가지고 제어각  $\alpha_1$ 과  $\alpha_2$ 로 각각의 사이리스터를 제어하는 것이 목적이다.

알파 제어기 (Alpha controller) 는 찾아낸 포인트에서 임의의 제어각  $\alpha_1$ 과  $\alpha_2$ 를 지정할 수 있는 컨트롤러이며 지정한 제어각  $\alpha_1$ 과  $\alpha_2$ 에서 사이리스터가 점호될 수 있도록 하고 이 때 지연된 점호가 시작되면 전류도 지연되어  $120^\circ$ 의 위상으로 흐르게 된다. 게이트 제어기 (Gate controller) 는 알파 제어기 (Alpha controller) 에서 각각 제어각 만큼 지연시킨 점호 신호가 사이리스터의 게이트로 입력되기 위한 과정을 거치면 최종적으로 사이리스터 브리지 회로의 제어가 완료 된다.

그림 3.1에서 게이트 제어기 (Gate controller) 는 영점을 찾아 Alpha가 만큼 점호를 지연 제어시켜 사이리스터의 게이트에 입력을 시키는 목적이다. 이 과정을 모두 거치게 되면 사이리스터 브리지 회로를 대칭 제어와비대칭 제어 목적에 맞게 사용할 수 있다.

# 3.3 시뮬레이션 및 실험

그림 3.2 초전도 에너지 저장 장치용 3상 사이리스터 브리지 구성

Fig. 3.2 3-phase thyristor bridge circuit configuation for SMES

Psim 프로그램을 사용하여 그림 3.2와 같이 회로도를 제작하였고 각 상을 R, S, T로 정의하여 선간전압을 검출하는 영점 검출기 (Zero crossing point detector) 로 영점을 검출하여 알파 제어기 (Alpha controller) 로 알파각을 제어하였고 최종적으로 게이트 제어기 (Gate controller) 로 사이리스터 게이트에 신호를 넣어주는 사이리스터 브리지 회로를 구성하였다. SMES에 해당하는  $X_L$ 은 저항성분이 없는 아주 큰 인덕터로 가정하여 회로에 부하로 가정하였고 Psim Simulation View로 결과를 확인하였다.

### 3.3.1 컨버터 모드 (Converter mode)

그림 3.3 컨버터모드의 대칭 제어  $lpha_1=0^\circ,lpha_2=0^\circ$ 의 출력 전압파형

Fig. 3.3 Output voltage waveform of symmetrical control in converter mode angle  $\alpha_1=0$  ° ,  $\alpha_2=0$  °

(a)  $\alpha_1 = 120^{\circ}$ ,  $\alpha_2 = 0^{\circ}$  (0 ~ 20 sec)

그림 3.4 컨버터 모드의 비대칭 제어  $lpha_1=120\,^\circ,lpha_2=0\,^\circ$ 의 출력 전압

Fig. 3.4 Output voltage waveform of asymmetrical control of converter mode angle  $\,\alpha_1=120\,^\circ$  ,  $\,\alpha_2=0\,^\circ$

Fig. 3.5 Hamonic analysis of output voltage and current with control of converter mode

- 54 -

# 3.3.2 인버터 모드 (Inverter mode)

(a)

$$\alpha_1 = 150^{\circ}$$

,  $\alpha_2 = 150^{\circ}$  (0 ~ 20 sec)

그림 3.6 인버터 모드의 대칭제어  $\alpha_1=150\,^\circ,\alpha_2=150\,^\circ$ 의 출력 전압

Fig. 3.6 Output voltage waveform of symmetrical control of inverter mode angle  $~\alpha_1=150~^\circ$  ,  $~\alpha_2=150~^\circ$

(a)  $\alpha_1 = 120\,^\circ$  ,  $\alpha_2 = 150\,^\circ$  (0 ~ 20sec)

그림 3.7 인버터 모드의 비대칭 제어  $\alpha_1=120\,^\circ$ ,  $\alpha_2=150\,^\circ$ 의 출력 전압 Fig. 3.7 Output voltage waveform of asymmetrical control of inverter mode angle  $\alpha_1=120\,^\circ$ ,  $\alpha_2=150\,^\circ$

Fig. 3.8 Hamonic analysis of output voltage and current with control of inverter mode

#### 3.4 결과 및 고찰

컨버터 모드에서 제어각  $\alpha_1$ 과  $\alpha_2$ 를 0 ° 로 대칭 제어하였을 경우는 그림 3.3과 같고 이와 비교하기 위해 제어각  $\alpha_1$ 을 120 ° 로 제어하고  $\alpha_2$ 를 0 ° 로 비대칭 제어하였을 때의 파형은 그림 3.4와 같다.

그림 3.5는 그림 3.3과 그림 3.4에서 대칭 제어를 하였을 때와 비대칭 제어를 하였을 때의 Psim 프로그램에서 고조파 분석을 실시한 결과이며, 대칭 제어를 할 경우 출력 전압은 입력 전압 주파수의 6배의 고조파를 기본파로 하는 고조파를 함유하고 있고 비대칭 제어를 하였을 경우 한 주기가 120° 간격으로 연속되어 출력 전압의 기본 주파수는 입력 주파수의 3배가 된다. 하지만 문제가되는 것은 전압보다 각 상의 입력 전류에 포함된 고조파가 시스템에 심각한 영향을 끼치게 되지만, A상의 주파수만 보았을 때, 직류 전류는 서로 상쇄되어 없어지는 것을 확인하였고 시뮬레이션 결과 3의 배수는 나타나지 않았다.

인버터 모드에서는  $\alpha_1$ 과  $\alpha_2$ 를 150°로 대칭 제어하였을 경우는 그림 3.6과 같고 이와 비교하기 위해 제어각  $\alpha_1$ 을 120°로 제어하고  $\alpha_2$ 를 150°로 비대칭 제어하였을 때의 파형은 그림 3.7과 같다.

그림 3.8은 그림 3.6과 그림 3.7에서 대칭 제어와 비대칭 제어를 하였을 때의고조파 분석을 실행한 것으로 컨버터 모드와 같게 대칭 제어를 할 경우 출력 전압은 입력 전압 주파수의 6배의 고조파를 기본파로 하고, 비대칭 제어를 하였을 경우 기본 주파수는 입력 주파수의 3배를 갖게 된다. 인버터 모드에서 입력전류의 고조파 분석에서도 3의 배수는 나타나지 않았다.

### 제 4 장 결 론

본 논문에서는 3상 사이리스터 브리지 회로에서 비대칭 제어를 이용하여 무효전력을 최소화하고 역률을 증가시켜 평균 출력전압을 제어하는 전력변환 기를 제안하였다.

제안한 시스템은 사이리스터 브리지에서 컨버터 모드로 비대칭 제어를 하였을 경우, 평균 출력 전압은 감소하지만 무효전력을 감소시켜 역률을 증가시킬 수 있었다. 인버터 모드에서도 비대칭 제어를 하였을 경우, 평균 출력 전압은 감소하지만 무효전력을 감소시켜 역률을 증가시킬 수 있었다. 또한 사이리스터 브리지에서 비대칭 제어는 평균 출력전압을 미세하게 조정할 수 있는 장점을 가지는 것을 확인할 수 있었다. 그래서 비대칭 제어를 통하여 유효전력을 감소시켜 역률을 증가시킬 수 있지만 시뮬레이션을 통하여 입력 전류에 고조파가 많이 부착되는 단점을 얻게 되었다.

본 연구를 통하여 사이리스터 브리지 회로에서 비대칭 제어를 하여 평균 출력 전압은 감소하지만 무효전력을 감소시켜 역률을 증가시키는 큰 장점을 가지지만 입력 전류에 고조파가 많이 부착되는 단점을 해결하기 위하여 사이리스터 브리지를 직병렬로 연결하여 부착된 고조파를 감소시켜 고역률 변환기로 연구를 발전시킬 계획을 갖게 되었다.

# 참 고 문 헌

- [1] I. S. Hong, "신재생 에너지 확대의 관건, 전력 저장장치", LG Business Insight 2010 7.7, Weekly 포커스, pp34-42.

- [2] A. R. Kim, H.R. Seo, G.H. Kim, M. Park, I.K. Yu, Y. Otsuki, J.Tamura, S. H. Kim, K. Sim, and K. C. Seong, "Operating Characteristic analysis of HTS SMES for frequency stabilization of dispersed power generation system", IEEE Trans. Appl. Supercond, Vol. 20, No.3, pp1334-1338, 2010

- [3] H.Y. Jung, A. R. Kim, J. H. Kim, M. Park, I. K. Yu, S. H. Kim. K. Sim, H. J. Kim, K. C. Seong, T. Asao, and J. Tamura, "Study on the operating characteristics of smes for the dispersed power generation system", IEEE Trans. Appl. Supercon., Vol.19, No.3, pp 2028-2031, 2009

- [4] 나가야 시게오, "초전도 순저보상 SMES의 개발", 전기평론, 2004

- [5] H. K. Yeom, D. Y. Ko, S. J. Park, U. J. Hong, H. B. Kim "에너지기계 기술 초전도 전력저장장치", State of the art report, Vol. 20, No.3, pp48-60, 2008.

- [6] S. Lee, "Magnetic Field Calculation of Toroidal Winding with Circular Section", Superconductivity and cryogenics Vol. 12, No.1, pp28-31, 2010

- [7] S. Lee, Y. Kim, S. H. Park, J. K. Lee, J. H. Bae, K. C. Seong, K. Choi, S. Hahn, "Design of an high Temperature Superconducting Magnet for a 5 MJ SMES", 대한전기학회 2011년도 제 42회 하계학술대회, pp. 894-895, July 20, 2011.

- [8] S. Lee, K. P. Yi, S. H, Park, J. K. Lee, W. S. Kim, C. Park, J. H. Bae, K. C. Seong, I. Park, K. Choi, and S. Hahn, "Design of HTS Toroidal Magnets for a 5 MJ SMES", IEEE Trans. Appl. Supercond, Vol. 22, No. 3, pp5700904, 2012

- [9] J. H. Kim, S. Y. Hahn, C. H. Im, J. K. Jung, and S. Y. Hahn, "Design of a 200-kJ HTS SMES System", IEEE Trans. Appl. Supercond., Vol. 12, No.1, pp 774-777, 2002

- [10] K. Kim, S. Lee, S. Kim, M. Park, I. K. Yu, J. K. Lee, S. Y, Lee, K.

- Choi, K. C. Seong, and H. Yeon, "Stress analysis for Toroid=Type HTS SMES coil and bobbin structure considering large parallel megnetic field", IEEE Trans. Appl. Supercond, Vol. 21, No. 3, pp 2275-2278, 2011.

- [11] V.R Stefanovic, "power factor Improvement with a modified phase controlled Converter." IEEE Trans., IA Vol-15, No.2, 1979

- [12] B.K. Bose, Power Electronics and AC drives. Prentice-Hall

- [13] S.B Dewan and A.S Straughen, Power Semiconductor Circuit. John Wily & Sons, Inc

- [14] P.C Sen and Murray L. MacDonald, "Thyristorized D.C Drives with Regenerative Braking and Speed Reversal.", IEEE Trans, Vol IECI-25 No.4, 1978

- [15] Pratap Mehta and Subhas R. Mukhopadhyay, "Improvement in DC Motor performance by Asymmetrical Triggering.", IEEE Trans. on Ind. Applications, Vol. IA-11, No.2 Mar/Apr. 1975

- [16] B.R Pelly, Thyristor phase-Controlled Converter and Cycloconverters.

John Wily & Sons, Inc

- [17] Guy Oliver, Victor R.Stefanovic, Georges-Emile April Guy Oliver, Victor R,Stefanovic, "Microprocessor Controller for a Thyristor Converter with an Improved Power factor." IEEE Trans. On Ind. Electronics and Control Instrument VOL. IECI-28 NO.3 Aug 1981

- [18] Guy Oliver, Victor R.Stefannovic, Geoges-Emile April "Thyristor Current Source with an Improved Power Factor." IEEE Trans. ON IND. Electronics VOL.IE-29, NO.4 Nov., 1982

- [19] Mark J. Kocher, Robert L.Steigerwald, "An AC-to-DC Converter with High Quality Input Waveforms." IEEE Trans. On Ind. Application VOL. IA-19, NO.4 July/Aug. 1983

- [20] Ali Mirbod, Ahmed EI-Amawya, "A General-Purpose Microprocessor-Based control Circuit for a Three-phase controlled Rectifier Bridge." IEEE Trans. on Ind, Electronics VOL. IE-33 No.3 Aug. 1986

- [21] Abraham Alexandrovitz, Alexander Yair, Eluid Epstein, "Analysis of a

- Static VAR Compensator with Optimal Energy Storage element." IEEE Trans. on Ind. Electronics Vol. Ie-31 No.1 Feb. 1984

- [22] Mohammad H. Rashid, All I. Maswood, "Analysis of Three-phase AC-DC Converters Under Unbalanced Supply conditions." IEEE Trans. On Ind. Applications VOL. 24, No.3 May/June 1988

- [23] Eduard Muljadi, Rich Schiferl, Thomas A.Lipo, "Induction Machine Phase Balancing by Unsymmetrical Thyristor Voltage Control.", IEEE Trans. On Ind. Applications Vol. IA-21, No.4 May/June 1985

- [24] Willian McMurracy, "A Study of Asymmetrical Gating for phase Controlled Converter." IEEE Trans. On Ind. Application VOL. IA-8, No.3, May/June 1972

- [25] R.L Kustom, James J. Skiles, J. Wang, J.Cleary, and F. Tsang, "Power Conversion System for Diurnal load leveling with Superconductive Magnetic Energy Storage." IEEE Trans. On Mag., Vol. Mag-23, No.5 Sep. 1987

- [26] Muhammad H. Rashid All I. Maswood, "A Novel Method of Harmonic Assessment Generated by Three-phase AC-DC Converter Under Unbalanced Supply condition." IEEE Trans. On Ind. Application VOL. 24 No.4 July/Aug. 1988

- [27] Noriaki Sato, Yoichi Hayashi, "Power Converter and Quench Protection to Superconducting Magnetic Energy Storage." Faculty of Engineering, Tokyo Institute of Technology, Tokyo 152, Japan

- [28] M.A Slonim, J.D. Van wyk, "Power Components in a system with Sinusoidal and Nonsinusoidal Voltages and/or Current". IEE Proceeding. Vol 135, Pt.B, No.2 Mar., 1988

- [29] S.A Hamed, Msc,PhD, Prof. B.J. Chalmers, Phd, Dsc, CEng, Fiee, "New method of Analysis and Performance Prediction for Thyristor Voltage-Controlled RL load.", IEE Proceedings, Vol. 134. Pt B, No.6 Nov. 1987

- [30] Gottfried Moltgen, Converter Engineering. Siemens Akfiengesellchaft John Wiley And Sons