# 工學碩士 學位論文

Ka대역의 이동성을 고려한 양방향 위성 방송통신융합 채널 전송방식 연구

A Study of Broadcasting Channel Transmit Scheme of Satellite Communication of Ka Band for Mobility

指導教授 鄭 智 元

2007年 2月 韓國海洋大學校 大學院 電 波 工 學 科 鄭 眞 姬

## 本 論文을 鄭眞姬 의 工學碩士 學位論文으로 認准함.

委員長 : 工學博士 金 基 萬

委 員 : 工學博士 李 炫 九

委 員 : 工學博士 鄭 智 元

2007年 02月 韓國海洋大學校 大學院

電波工學科

鄭 眞 姬

# 목 차

| 그림 목차                                             | iii             |

|---------------------------------------------------|-----------------|

| 표 목차                                              | vi              |

| ABSTRACT                                          | vii             |

| 제 1 장 서론                                          | 1               |

| 제 2 장 규격서 분석                                      | 2               |

| 제 2-1 절 DVB-T 규격서 분석                              | 3               |

| 제 2-2 절 DVB-H 규격서 분석                              | 10              |

| 2.2.1. Time Slicing                               | 12              |

| 2.2.2. Time Interleaving                          | 12              |

| 2.2.3. Unequal Error Protection (UEP)             | 13              |

| 2.2.4. Multi Protocol Encapsulation Forward Error | Correction (MPE |

| -FEC)                                             | 13              |

| 제 2-3 절 DVB-S2 규격서 분석                             | 14              |

| 2.3.1. LDPC 부호                                    | 14              |

| 제 3 장 이동성 DVB-S2 알고리즘                             | 18              |

| 제 3-1 절 FIFTH 제안모델                                | 18              |

| 3.1.1. Train interruption 채널 모델링 방법               | 18              |

| 3.1.2. FIFTH 제안 모델 I                              | 20              |

| 3.1.3. FIFTH 제안 모델 II                             | 22              |

| 제 3-2 절 DVB-S2M 제안 모델                             | 25              |

| 3.2.1. Virtual Interleaver                        | 25              |

| 3.2.2. Time Interleaver                           | 26              |

| 제 3-3 절 제안한 Interleaver 모델                        | 29              |

| 제 4 장 시뮬레이션 및 성능 평가                                     | 31 |

|---------------------------------------------------------|----|

| 제 4-1 절 시뮬레이션 채널 환경                                     | 32 |

| 제 4-2 절 기존의 block interleaver와 제안된 block interleaver의 성 | 능  |

| 비교                                                      | 34 |

| 제 4-3 절 AWGN 채널 환경에서 성능 평가                              | 37 |

| 제 4-4 절 TI(Train Interruption) 환경 하에서 성능 평가             | 42 |

|                                                         |    |

| 제 5 장 결론                                                | 49 |

|                                                         |    |

| 참고문헌                                                    | 51 |

# 그림목차

| 그림 | 2-1. DVB-T baseline system 블록도                       | 4  |

|----|------------------------------------------------------|----|

| 그림 | 2-2. 데이터 패킷 구조                                       | 4  |

| 그림 | 2-3. 외부 interleaver와 de-interleaver의 기능 블록도          | 5  |

| 그림 | 2-4. Non-hierarchical 전송 mode의 비트 맵핑                 | 6  |

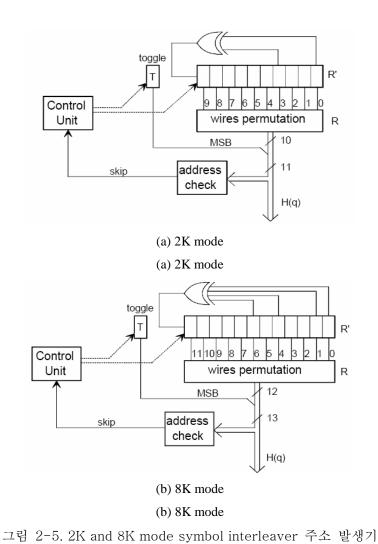

| 그림 | 2-5. 2K and 8K mode symbol interleaver 주소 발생기        | 9  |

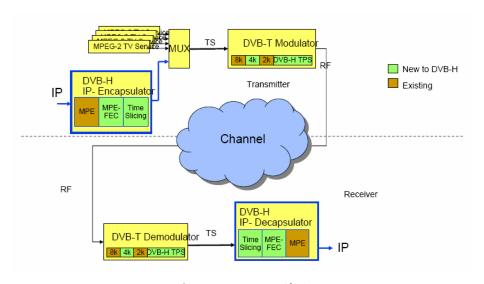

| 그림 | 2-6. DVB-H 블록도                                       | 11 |

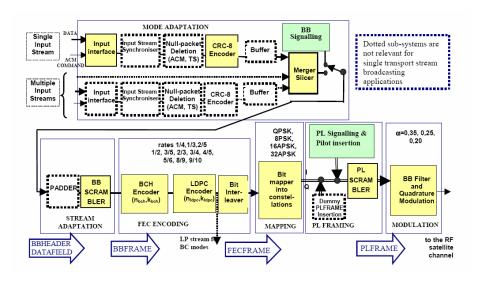

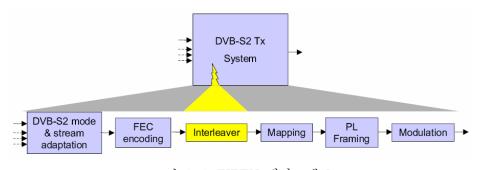

| 그림 | 2-7. DVB-S2 시스템 블록도                                  | 14 |

| 그림 | 2-8. Submatrix of Parity Check Matrix                | 15 |

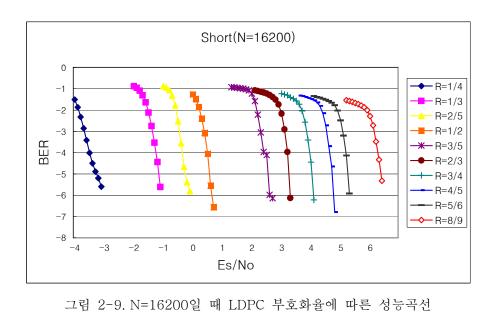

| 그림 | 2-9. N=16200일 때 LDPC 부호화율에 따른 성능곡선                   | 17 |

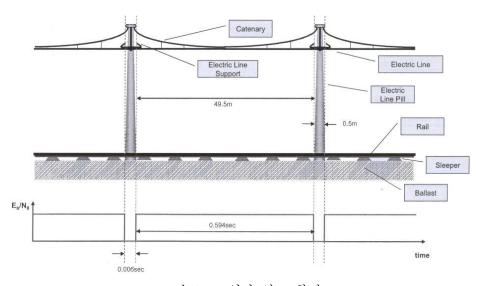

| 그림 | 3-1. 열차 선로 환경                                        | 18 |

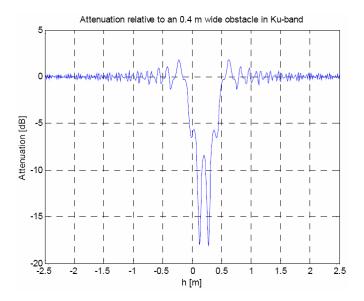

| 그림 | 3-2. Train interruption 감쇄                           | 19 |

| 그림 | 3-3. FIFTH 제안모델 I                                    | 21 |

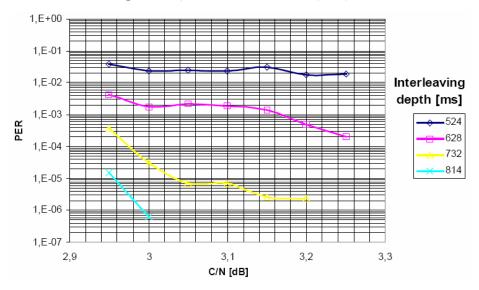

| 그림 | 3-4. Interleaving 길이에 따른 FIFTH 모델 I의 성능              | 21 |

| 그림 | 3-5. FIFTH제안 모델 II                                   | 22 |

| 그림 | 3-6. QPSK + 2/3 + RS(1023,975,48)                    | 23 |

| 그림 | 3-7. QPSK + 3/4 + RS(255,191,64)                     | 23 |

| 그림 | 3-8. QPSK + 3/4 + RS(223,191,32)                     | 24 |

| 그림 | 3-9. QPSK + 2/3 + RS(209,191,18)                     | 24 |

| 그림 | 3-10. DVB-S2M 제안 모델                                  | 25 |

| 그림 | 3-11. MPE-FEC 프레임 구조                                 | 26 |

| 그림 | 3-12. PL#2 time interleaving                         | 27 |

| 그림 | 3-13. PL#1 block interleaving 구조                     | 29 |

| 그림 | 4-1. AWGN과 TI환경에서 DVB-S2 성능평가                        | 32 |

| 그림 | 4-2. UL 부호방식 성능 분석                                   | 33 |

| 그림 | 4-3. 기존의 block interleaver와 제안한 block interleaver의 성 | 능비 |

| 교  |                                                      | 35 |

| 그림 4-4. 기존의 block interleaver와 제안한 block interleaver의 성능비         |

|-------------------------------------------------------------------|

| <u></u>                                                           |

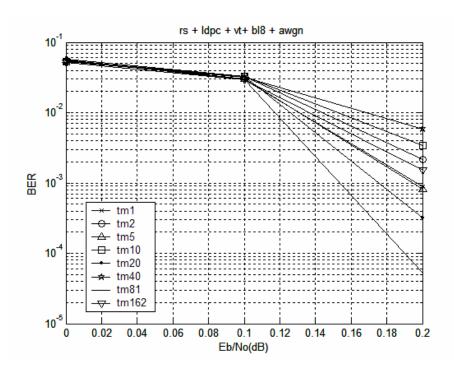

| 그림 4-5. AWGN 환경 하에서 LDPC(R=1/2), Block interleaver의 크기가           |

| 8 일 때, time interleaver 크기에 따른 성능37                               |

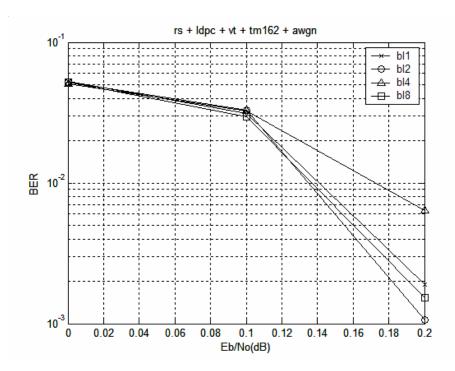

| 그림 4-6. AWGN 환경 하에서 LDPC(R=1/2), time interleaver 크기 162          |

| 일 때, block interleaver의 크기에 따른 성능                                 |

| 그림 4-7. AWGN 환경 하에서 RS(255,191,64), LDPC(R=1/2), block            |

| interleaver의 크기 8, time interleaver의 크기 162 일 때, virtual          |

| interleaver 유무에 따른 성능39                                           |

| 그림 4-8. AWGN 환경 하에서 RS(255,191,64), LDPC(R=1/2), block            |

| interleaver의 크기 8, virtual interleaver가 존재할 때, time interleaver의  |

| 크기에 따른 성능40                                                       |

| 그림 4-9. AWGN 환경 하에서 RS(255,191,64), LDPC(R=1/2), virtual          |

| interleaver 존재, time interleaver의 크기 162일 때, block interleaver의   |

| 크기에 따른 성능41                                                       |

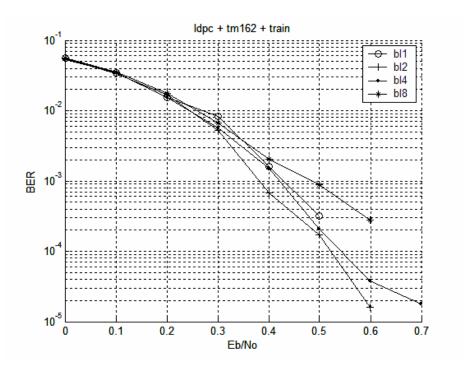

| 그림 4-10. Train interruption 환경 하에서 LDPC(R=1/2), time              |

| interleaver 크기 162 일 때, block interleaver 개수에 따른 성능42             |

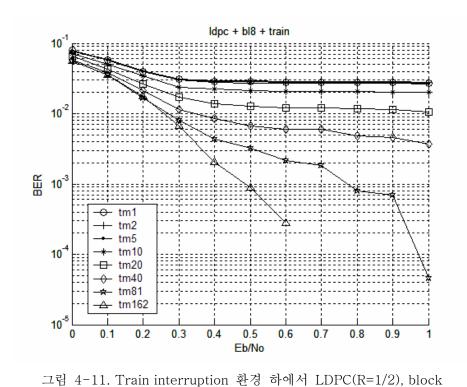

| 그림 4-11. Train interruption 환경 하에서 LDPC(R=1/2), block             |

| interleaver 크기 8일 때, time interleaver의 크기에 따른 성능43                |

| 그림 4-12. Train interruption 환경 하에서 RS(255,191,64),                |

| LDPC(R=1/2), Block interleaver의 크기 8, time interleaver의 크기 162    |

| 일 때, virtual interleaver 유무에 따른 성능44                              |

| 그림 4-13. Train interruption 환경 하에서 RS(255,191,64),                |

| LDPC(R=1/2), virtual interleaver, block interleaver 크기 1일 때, time |

| interleaver의 크기에 따른 성능45                                          |

| 그림 4-14. Train interruption 환경 하에서 RS(255,191,64),                |

| LDPC(R=1/2), block interleaver의 크기 1, virtual interleaver가 존재할    |

| 때, time interleaver의 크기에 따른 성능                                    |

| 그림 4-15. Train interruption 환경 하에서 RS(255,191,64               | ), |

|----------------------------------------------------------------|----|

| LDPC(R=1/2), virtual interleaver 존재, block interleaver 크기 8일 미 | 대, |

| time interleaver의 크기에 따른 성능                                    | 47 |

| 그림 4-16. Train interruption 환경 하에서 RS(255,191,64               | ), |

| LDPC(R=1/2), time interleaver가 162일 때 block interleaver 크기에    | 따  |

| 른 성능                                                           | 48 |

# 표 목 차

| 끂 | 2-1. 2K mode의 비트 순열                      | .8 |

|---|------------------------------------------|----|

| 丑 | 2-2. 8K mode의 비트 순열                      | .8 |

| 丑 | 2-3. 코딩 파라메타 (n <sub>ldpc</sub> = 64800) | 16 |

| 丑 | 2-4. 코딩 파라메타(n <sub>ldpc</sub> =16200)   | 16 |

| 丑 | 3-1. FIFTH 제안모델 사양                       | 22 |

| 丑 | 3-2. PL#2 time interleaving 사양2          | 28 |

| 莊 | 3-3. PL#1 block interleaver 사양           | 30 |

### **ABSTRACT**

In the beginning of satellite broadcasting systems, concatenate coding schemes are considered as being the best solution for powerful protection of digital information against nonlinear distortion and fading noise. However, the performance of concatenate coding scheme is away from Shannon's limit. The emergence of the iteration decoding algorithms such as turbo codes and Low Density Parity Check (LDPC) codes has changed our view of the Shannon capacity, the capacity has become a practical benchmark for a coding system not only for power limited channels but also for bandwidth channels. Therefore, the high definition television (HDTV) satellite standards, known as The Digital Video Broadcasting (DVB-S2) transmission system employs a LDPC coding technique as a channel coding scheme.

Recently, an important issue is DVB-S2 system for mobility. The Fast Internet for Fast Train Hosts (FIFTH) project in Europe aims at providing digital TV and internet services to passengers of high-speed trains based on DVB-S. To take into account the possibility offered by the DVB-S2 specifications, the FIFTH project decided to carry out investigation on the possibility to replace DVB-S with DVB-S2 in the FIFTH forward link. Since DVB-S2 has been defined for a fixed satellite channel, no countermeasures are present in the system architecture for the system to properly work in presence of long deep fading events. In deep fading channel, since error bursts are spreading before DVB-S2 system, additional cascaded co-decoders are needed while maintaining spectral efficiency. The channel interleaving and Reed Solomon coding technique are required. This solution will be adopted in the DVB-H standard currently under preparation, to adapt

the DVB-T standard for mobile reception. Therefore, this thesis analyzes the modified DVB-S2 system to adapt DVB-H and DVB-T for mobile reception by satellite broadcasting system.

This thesis organized as follows. In section 2, several DVB specifications are analyzed. Section 3 describes DVB-S2 for mobility and Section 4 shows simulation results. Finally, section 5 gives conclusion.

# 제 1 장 서 론

기존의 연접부호는 높은 부호이득을 얻어낼 수 있으며, 무선통신시스템에서 각광을 받고 있으나 이의 성능이 Shannon's Limit와 다소 큰 격차를보이고 있다. 또한, 우수한 성능을 만족하면서 강우 감쇠 그리고 채널 페이당 환경에서 지속적인 방송을 가입자에게 제공하기 위해서는 성능이 우수한 채널 부호화 방식의 적용이 필수적이다. 이에 따라 최근 HNS사에서 제안한 DVB-S2 표준화 등에서 논의되고 있는 LDPC (Low Density Parity Check) 부호와 결합한 연접 채널 부호화 방식의 연구 또한 활발히 진행중이다.

또한 차세대 위성통신은 소형 이동형 지상파 방송 및 고정형 지상파 방송과 위성과의 융합에 관한 연구가 활발히 진행 중에 있으며, 특히 이동체에 대한 위성 방송 및 인터넷 통신을 하기 위한 연구가 제안되고 있다. 전세계적으로 FIFTH (Fast Internet for Fast Train Host) 프로젝트가 현재이동체 위성 방송분야에 연구가 활발히 진행되고 있다. 이의 연구를 위해서는 우수한 성능을 만족하면서 가입자가 이동하더라도 방송을 지속적으로제공하기 위해 DVB-S2 표준화 등에서 논의되고 있는 LDPC (Low Density Parity Check) 부호와 interleaver, 외부 부호와 결합한 새로운 부호화 방식의 연구가 필수적이다. 이의 정확한 성능 평가를 위해서는 DVB-S2 시스템과 이동체에 대한 통신 규격인 DVB-T, DVB-H를 결합한이동체에 대한 위성 방송, 위성 인터넷 통신을 위해 채널 모델링, 이동중인물체의 속도, 터널에서의 deep fading환경에서도 통신이 가능한interleaver의 구조 등이 필수적으로 연구되어야 한다.

따라서 본 논문에서는 DVB-S2를 근간으로 하는 LDPC의 Short frame 의 적용을 기본으로 할 때 이동체 위성 통신을 위한 채널 부호화 기법에 대한 연구를 하였고, interleaver 및 DVB-S2와 결합한 interleaver 크기및 RS 부호의 오류정정 능력에 대해 성능 분석과, deep fading 채널에 대한 대처 방안에 대해 연구하였다.

# 제 2 장 규격서 분석

최근 디지털 방송과 이동 통신의 융합 추세 및 이동 통신 시스템의 비약 적인 발전에 힘입어 디지털 방송 시스템은 고정 수신만을 고려하여 설계되 었던 초기 시스템에서 이동성뿐만 아니라 휴대성을 고려한 시스템으로 진 화되어 가고 있다. 유럽의 지상파 디지털 방송시스템의 표준안인 DVB (Digital Video Broadcasting) 시스템은 위성, 케이블, 지상파 등 모든 전 송에서 디지털 TV 및 데이터 방송을 위한 완전한 해결방안을 제시하였다. DVB 표준으로는 위성방송의 대표적인 DVB-S, DVB-S2와 지상파 방송의 대표적인 DVB-T가 있다. 또한 고정 수신만을 고려하여 수신되었던 초기 시스템에 이동성 및 휴대성으로 진화되고 있는 가운데 DVB-T를 기반으로 하는 DVB-H의 표준화로 진행되고 있다. 현재 국내에서는 위성 및 지상파 DMB (Digital Multimedia Broadcasting)를 통한 방송 서비스가 제공되고 있으며, 유럽에서는 기존의 DVB-T (Digital Video Broadcasting-Terrestrial) 표준을 기반으로 소형 휴대 단말기에 적합한 DVB-H(handheld)의 표준화를 진행하고 있다. 본 장에서는 이러한 표준안에서 적용되고 있는 오류정정부호의 사례를 분석하고자 한다.

### 제 2-1 절 DVB-T 규격서 분석

DVB(Digital Video Broadcasting)는 유럽형 디지털 방송의 표준으로 기존의 위성(DVB-S), 유선(DVB-C), 지상파(DVB-T) 인프라를 이용하여 MPEGII 포맷의 디지털 TV 서비스를 위한 틀을 제공하였다.

DVB-T는 지상파 방송에 적합한 Orthogonal Frequency Division Multiplex (OFDM) 방식을 사용한다. DVB-T는 네트워크 성격에 따라서 2K/8K mode를 지원하는데, 2K는 1705개의 서브 채널에 심볼을 나누어 전송하고, 8K는 6817개의 서브 채널에 심볼을 나누어 전송한다.

DVB-T는 VHF/UHF 대역에서 동작하므로, 지상파 환경에서 발생하는 fading, multipath propagation, 채널의 불완전한 특성과 여러 가지 장애로 인한 Co-Channel Interference (CCI)와 Adjacent Channel Interference (ACI)에 대한 충분한 보호가 필요하다. 채널 상의 에러를 정정하기 위한 오류 정정 방법으로 연접 오류 정정 코드 (Concatenated Forward Error Correction)를 사용한다. 수신단에서는 이러한 오류를 정정하기 위해서 외부 부호화(outer coding)로 RS(Reed-Solomon) coding을 내부 부호화 (inner coding)로 길쌈 부호화(convolution coding)를 사용한다.

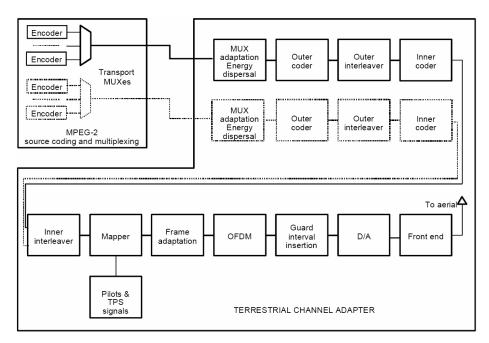

그림 2-1에 DVB-T 시스템의 송신부의 전체적인 블록도를 나타내었다. 두 가지 계층구조 (hierarchical mode)로 전송하기 위해 splitter를 거친 MPEG-2 데이터는 독립적인 오류 정정 부호화기(FEC: Forward Error Correction)를 거친다. 먼저 에너지의 분산을 목적으로 난수화(randomize)된 데이터를 외부 RS 부호화기를 거친 다음 내부 길쌈 부호화를 한다. 각각의 채널 부호화 후에는 연집 에러(burst error)가 발생할 때를 대비하여 interleaving을 하게 된다. Interleaving 된 데이터는 QPSK, different level 16QAM, 64QAM 등으로 변조를 한 후, 2K mode일 때 1705, 8K mode일 때 6817개의 채널에 변조된 심볼을 나누어 OFDM 방식으로 전송된다.

그림 2-1. DVB-T baseline system 블록도

Fig. 2-1. DVB-T baseline system block diagram

DVB-T 시스템은 위성, 케이블을 이용한 서비스와 호환성을 유지하기 위하여 외부코딩과 외부 interleaving은 공통으로 한다. 또한 2K mode와 8K mode가 있는데 2K mode는 단일 전송기 운용 망과 제한된 전송거리를 갖는 작은 SFN 망에 적당하고, 8K mode는 단일 전송기 운용 망과 큰 SFN 망 모두 사용될 수 있으며 채널 환경에 맞는 전송 비트 율을 설정하기 위하여 다양한 부호화 율과 다양한 레벨을 갖는 변조 방식을 포용한다.

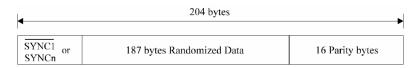

그림 2-2. 데이터 패킷 구조

Fig. 2-2. Data packet structure

DVB-T시스템에서 사용한 외부 코딩은 축소된 RS(204,188,t=8) 코드를 사용하며 이 코드는 RS(255,239,t=8) 코드를 이용하여 쉽게 얻을 수 있다. 그림 2-2와 같이 외부 코딩을 이용하여 16바이트의 오류 검출 코드를 생성하여 정보 데이터 188 바이트를 포함, 총 204 바이트의 출력 값을 얻게된다. 이 외부 코딩을 이용하여 총 8 바이트의 오류를 검출, 복원 시킬 수 있다.

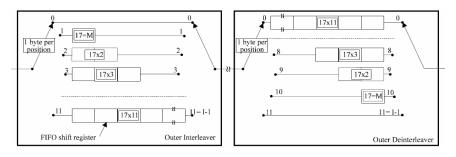

그림 2-3. 외부 interleaver와 de-interleaver의 기능 블록도

Fig. 2-3 Outer interleaver and de-interleaver block diagram

외부 interleaver는 그림 2-3과 같이 "Forney" 방식의 convolutional interleaver를 사용하여 동기워드 혹은 반전된 동기워드로 시작되는 204 바이트 단위의 패킷을 interleaving을 한다. 12개의 branch로 구성되어 있으며 각 branch는 17 bytes x n, (n=0, 1, 2, ..., 11) 단위의 셀들로 각각 구성되며 입출력 스위치는 서로 동기되어 동작한다.

DVB-T 시스템은 부호화율 1/2과 64 state 길쌈 코드를 기반으로 한 다양한 비율의 심벌탈락 길쌈 코드를 제공한다. 이렇게 함으로써 다양한 서비스와 데이터 전송률에 따라 적절히 부호화율(1/2, 2/3, 3/4, 5/6, 7/8)을 정할 수 있다. 기반이 되는 코드의 생성 다항식은  $G_1$ = $171_{oct}$  와  $G_2$ = $133_{oct}$ 이다.

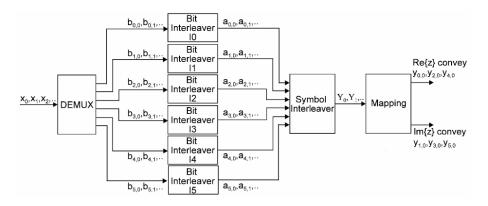

그림 2-4. Non-hierarchical 전송 mode의 비트 맵핑

Fig. 2-4. Bit mapping for non-hierarchical transmit mode

내부 interleaving은 bit interleaving과 symbol interleaving으로 구성되고 변조레벨에 따라 bit interleaver의 개수를 선택하여 사용한다. 그림 2-4에서 interleaver의 입력 비트  $X_d$ 는 아래의 식 2.1과 같이 된다.

$$X_{di} = b_{di(\text{mod})v.di(div)v}$$

$$di = \text{the input bit number}$$

(2.1)

여기에서 v=2(QPSK), v=4(16QAM), v=6(64QAM) 이다.

Bit interleaver의 블록 크기는 126 비트이고 각각의 bit interleaver의 입력 비트 벡터는 다음 식 2.2와 같이 정의된다.

$$B(e)=(b_{e.0},\,b_{e.1},\,b_{e.2},\,b_{e.3},...,\,b_{e.125}) \equiv (2.2)$$

여기서  $e=\{0,\,\,\cdots\,\,,\,\,v-1\}$  이다.

또한 interleaving된 출력 벡터 A(e) = (a<sub>e.0</sub>, a<sub>e.1</sub>, a<sub>e.2</sub>, a<sub>e.3</sub>, ···, a<sub>e.125</sub>) 는 다음 식 2.3과 같이 정의된다.

$$a_{e.w} = b_{e.He(w)} \tag{2.3}$$

여기서 w = 0, 1, 2, 3, ··· , 125 이다.

He(w)는 각 interleaver의 순열함수이고 다음 식 2.4와 같이 나타낼 수 있다.

$$I0: H_0(w) = w$$

$$I1: H_1(w) = (w + 63) \mod 126$$

$$I2: H_2(w) = (w + 105) \mod 126$$

$$I3: H_3(w) = (w + 42) \mod 126$$

$$I4: H_4(w) = (w + 21) \mod 126$$

$$I5: H_5(w) = (w + 84) \mod 126.$$

(2.4)

Symbol interleaver를 하는 목적은 bit interleaving된 비트 열들을 1512 (2K mode), 또는 6048 (8K mode)개의 캐리어들로 그룹핑 하기 위함이다. Symbol interleaver는 1512개의 데이터 심벌에 대하여 interleaving을 수행한다.

2K mode에서는 bit interleaving된 데이터  $12 \times 126$ 개를 순서적으로 읽어 symbol interleaver의 입력 벡터  $Y' = (y'_0, y'_1, y'_2, y'_3, \cdots, y'_{1511})$ 를 만들고, 8K mode에서는 bit interleaving된 데이터  $48 \times 126$ 개를 순서적으로 읽어 symbol interleaver의 입력 벡터  $Y' = (y'_0, y'_1, y'_2, y'_3, \cdots, y'_{6047})$ 를 만든다.

Symbol interleaving된 벡터 Y =  $(y_0, y_1, y_2, y_3, \cdots, y_{Nmax-1})$ 는 다음 식 2.5와 같이 정의된다.

$$\begin{aligned} y_{H(q)} &= y'_{q} \text{ for even symbols for } q = 0,..., Nmax - 1 \\ y_{q} &= y'_{H(q)} \text{ for odd symbols for } q = 0,..., Nmax - 1 \end{aligned} \tag{2.5}$$

여기서 Nmax는 2K mode일 경우1512이고, 8K mode일 경우6048이다.

H(q)는 다음 식 2.6과 같이 정의되는 순열함수 이다.

$$\begin{aligned} \mathbf{q} &= 0; \\ &\text{for } (\mathbf{I} = 0; \mathbf{I} < \mathbf{N} \max; \mathbf{I} + = 1) \\ &\{ \\ &H(q) = (i \mod 2) \cdot 2^{N_r - 1} + \sum_{j=0}^{N_r - 1} R_i(j) \cdot 2^j \\ &\quad if (H(q) < N_{\max}) q = q + 1; \\ &\} \end{aligned} \tag{2.6}$$

여기서 Nr =  $\log_2 Mmax$ , 2K mode일 경우에는 Mmax = 2048이고, 8K mode일 경우에는 Mmax = 8192이다.

2K mode일 경우와 8K mode일 경우의  $R_i(j)$ 를 표 2-1과 2-2에 정의하였고, 표에 표시된  $R'_i$ 는 다음 식 2.7과 같이 정의된다.

R'i는 Nr-1 개의 비트 크기를 갖는다. 예를 들어 2K mode에서는 10 비트의 크기를 갖는다.

$$\begin{split} &i=0,1; & R'_{i}\left[Nr-2,Nr-3,...,1,0\right]=0,0,...,0,0 \\ &i=2: & R'_{i}\left[Nr-2,Nr-3,...,1,0\right]=0,0,...,0,0 \\ &2 < I < Nmax: R'i[Nr-3,Nr-4,...,1,0]=R'i[Nr-2,Nr-3,...,1] \end{split}$$

in the 2K mode:  $R'_{i}[9] = R'_{i-1}[0] \oplus R'_{i-1}[3]$

in the 8K mode:  $R'_{i}[11] = R'_{i-1}[0] \oplus R'_{i-1}[1] \oplus R'_{i-1}[4] \oplus R'_{i-1}[6]$

#### 표 2-1. 2K mode의 비트 순열

Table 2-1. Bit permutations for the 2K mode

| R'i bit positions(j)                  | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------------------------------|---|---|---|---|---|---|---|---|---|---|

| R <sub>i</sub> bit positions(rule[j]) | 0 | 7 | 5 | 1 | 8 | 2 | 6 | 9 | 3 | 4 |

### 표 2-2.8K mode의 비트 순열

Table 2-2. Bit permutations for the 8K mode

| R'i bit positions(j)                  | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------------------------------|----|----|---|---|----|---|---|---|---|---|---|---|

| R <sub>i</sub> bit positions(rule[j]) | 15 | 11 | 3 | 0 | 10 | 8 | 6 | 9 | 2 | 4 | 1 | 7 |

상기 심볼 interleaving 알고리즘을 도식적으로 표현하면 그림 2-5와 같다.

Fig. 2-5. Symbol interleaver address generator for 2K and 8K mode

### 제 2-2 절 DVB-H 규격서 분석

DVB-T의 이동성 실험을 실시하는 중 다른 이동 멀티미디어 응용 서비스의 적용 가능 여부에 의문이 제기되었으며, DVB-T가 휴대폰 방송용으로는 취약점이 있다는 점을 조기에 발견하여, DVB-T를 기반으로 한 휴대용 기기를 위한 새로운 DVB 표준을 마련하게 되었다. 이것이 바로 DVB-H로 DVB-T 표준에 기반으로 하였기 때문에 DVB-T와 대부분 호환가능하나, 작고, 가볍고, 휴대형이고, 배터리로 동작되는 단말기 들의 성질을 고려하였다. DVB-H는 거의 모든 일반 단말기에서 수신 가능한 고속 downstream 채널을 지원함으로써 이동통신 네트워크를 개선시킨다. 따라서, DVB-H는 전통 방송 시스템과 Cellular 라디오 네트워크 사이에 다리를 놓아주는 역할을 하게 된다. DVB-H가 제공하는 광대역, 고속 downstream 채널은 Mbps 대에 달하는 데이터 전송률을 지원하며, 이는 오디오/비디오 Streaming, 파일 전송과 같은 다양한 서비스 응용을 가능하게 한다. 이 시스템은 휴대형 단말기에 서비스를 새로운 방식으로 배포할수 있게 하여 컨텐츠 제공자와 네트워크 운영자에게 다양한 가능성을 제시할 수 있다.

수신 환경에 열악한 환경을 위해 Link 계층에 오류보호 기능으로 Reed-Solomon (RS) 코드와 Block Interleaver로 구성된 MPE-FEC (Multi-Protocol Encapsulation Forward Error Correction)이 추가되었으며, 이는 기존의 DVB-T Channel Coding 위에 다시 Channel Coding을 함으로써 Time Interleaving 기능을 어느 정도 제공하고, DVB-T 전송 네트워크와의 호환성을 위해 관련된 모든 데이터 처리는 Transport Stream Interface 이전에 이루어진다. 그림 2-6은 DVB-H의 블록도를 나타낸다.

그림 2-6. DVB-H 블록도

Fig. 2-6. DVB-H block diagram

Multiplex에 포함된 DVB-H Elementary Stream의 파라미터 Signaling은 DVB-T 표준의 Transmission Parameter Signaling (TPS) 채널에 대한 확장을 사용한다. TPS는 별도의 정보 채널을 생성하여 수신기에게 튜닝 Parameter를 제공한다. TPS 채널의 새로운 요소들은 multiplex 내에 time slicing된 DVB-H Elementary Stream이 존재하는지에 대한 정보와 MPE-FEC보호가 최소한 하나의 Elementary Stream에 사용되고 있는지에 대한 정보를 제공한다.

DVB-H는 DVB-T가 지원하는 2K와 8K Mode를 포함하여 단일주파수 망(SFN) 구축을 위해서 4K Mode라는 네트워크 Mode를 추가적으로 지원하며, 이는 이동수신에 적합하고 여러 서비스 수신을 개선하는 Enhanced Signaling Channel을 제공한다. 사양을 충족시키는 DVB-H 단말기는 8K mode를 지원하며, 8K symbol interleaving를 포함한다. 4K mode는 DVB-H 전용 네트워크에서만 사용할 수 있으며, 나머지 두 mode에 대한 절충 안이며, 2K mode와 비교해서 SFN에서 송신기 거리를 2배 늘릴 수 있고, 8K mode 대비 이동 수신 시 Doppler Shift의 역효과에 대해 덜 민감하다.

휴대성을 고려한 방송 수신용단말기는 단말의 소형화 및 전력 소모 감소가 필수적으로 요구된다. 특히 기존의 이동전화기와 융합된 단말을 이용하기 위해서는 디지털 방송 신호 모뎀 칩에 따른 전력 소모를 최소화 해야만한다. 전력 소모를 최소화하기 위하여 전송 데이터를 일정한 time slot으로 구성한 후 각 time-slicing 기술을 활용한다. 일정한 전송률을 가지고 지속적으로 전송(streaming)되던 기존의 DVB-T 시스템과 달리 DVB-H는 향상된 압축 기술로 높은 전송률을 가지는 burst를 time-slicing 기법으로일정 간격 마다 전송하므로, 방송 신호를 수신 하지 않을 경우에는 수신단말을 절전하여 전력 소모를 줄일 수 있다. 그러나 이 경우 각 burst 마다 수신 신호에 대한 동기가 요구되며, 동기 수행에 소요되는 시간이 길어지게 되면 수신기의 전력 소모가 증가하므로 동기 수행 시간을 최소화하는 것이 중요하다.

### 2.2.1. Time Slicing

DVB-H에서 수신기의 전력 소모를 최소화하기 위하여, time Slicing 방식을 사용한다. DVB-H를 이용할 경우, 해당 서비스가 전송되지 않는 시간동안 수신기가 커진 그 시간만큼의 배터리의 전력을 절약이 가능하다는 것이다. 또한, 이를 통해 수 millisecond 또는 수 second 동안의 가변적 형태의 burst 데이터로 여러 개의 서비스 제공이 가능하다.

### 2.2.2. Time Interleaving

DVB-H는 고속 이동 통신을 위해 설계되지 않은 DVB-T 표준을 기반으로 설계되어 time Interleaving을 사용하지 않는다. DAB는 이동 수신을 고려하여 설계되어 time Interleaving을 사용하며, 이를 통해 한 개의 안테나를 사용하여 이동 수신을 할 경우 발생하는 fading 현상을 해결해준다. Time Interleaving은 burst오류를 보다 ms 시간 척도로 분포시켜 FEC가오류를 정정할 수 있게 한다. 이동 수신에서는 single 오류보다 burst 오류가 발생할 확률이 크기 때문이다. DAB에서 time Interleaving은 16개 데

이터 burst에 적용되며, 하나의 burst가 24ms이므로 time interleaving은 384ms 동안 적용된다.

### 2.2.3. Unequal Error Protection (UEP)

DAB는 decoding 과정에서 보다 중요한 위치를 차지하는 중요도가 높은 비트와 중요도가 낮은 비트를 구분하여 보호할 수 있는 UEP를 지원하며, decoding 과정에 미치는 영향에 따라 비트들의 중요도가 결정되고 보호된다. UEP를 사용할 경우, 메인 서비스 보호와 관련하여 다양한 오류보호 class들을 설계함으로써 fail이 발생하는 특징에 대해서 객관적 또는 주관적 서비스 품질 측면을 반영하여 최적화할 수 있다. DVB-H는 UEP가 제공되지 않는다. 이는 중요한 정보에 대해서도 최소한의 오류 보호만이 제공됨을 의미한다. 사용자 입장에서는 중요도가 낮은 비트들이 파괴되는 것에 대해서는 그다지 큰 문제가 발생하지 않으나, 자칫 이로 인해 수신신호의 동기가 어긋날 경우 심각한 문제가 발생 할 수도 있다.

# 2.2.4. Multi Protocol Encapsulation Forward Error Correction (MPE-FEC)

DVB-H에서는 한 개의 안테나를 사용하여 이동 수신을 높이기 위해 MPE와 추가적인 FEC를 사용하고 있으며, 이러한 오류 보호는 하나의 Time Slicing 안에서만 유효하다. 그러나, 무선상의 오류는 일박적으로 하나씩 발생하지 않으며 burst하게 발생하기 때문에 time slice가 자주 오류에 노출된 경우, 해당 서비스는 다음 time slice가 전송될 때까지 정지된다. MPE-FEC는 상위 프로토콜 계층에서 발생하는 잔여 오류를 부분적으로 수정한다. 따라서 DVB-H는 중요한 비트들에 대한 개별 보호 기능을 가지고 있지 않다.

### 제 2-3 절 DVB-S2 규격서 분석

DVB-S2 규격은 Ka 밴드 위성 방송 시스템을 위한 규격으로 DVB-S의 연접부호방식 대신 LDPC와 BCH를 연접시킨 부호화 방식을 채택하여 Ka 밴드 통신의 강우 감쇄 등의 페이딩으로 인한 성능 감소를 보완시켰다. 아래 그림 2-7은 DVB-S2의 블록 다이어그램이다.

그림 2-7. DVB-S2 시스템 블록도

Fig. 2-7. DVB-S2 system block diagram

### 2.3.1. LDPC 부호

DVB-S2 LDPC 코드의 parity check matrix는 sparse할 지라도 일반적인 generator matrix는 encoding을 위하여 필요하다. 물론, 일반적인 linear code는 parity check matrix를 알고 있기에 generator matrix는 Gaussian elimination method를 사용하여 간단하게 유도될 수 있다. 그러나 그 결과 generator matrix는 더 이상 sparse하지 않다. 이것은 저장 용량과 encoding complexity 문제를 야기한다. 따라서 여기서는 parity

check matrix를 다음 식 2.8의 형태로 적용시킨다.

$$H_{(N-K)xN} = \left[ A_{(N-K)xK} B_{(N-K)x(N-K)} \right]$$

(2.8)

여기서 B는 다음 그림 2-8의 형태이며 이는 Low Triangular parity check Matrix를 나타낸다.

그림 2-8. Submatrix of Parity Check Matrix

Fig. 2-8. Submatrix of Parity Check Matrix

Matrix A는 cycle-4를 피하고, cycle-6을 최소화 시키면서 sparse 하게 matrix을 구성하며, 각각의 초기치도 random하게 분포시킨다.

LDPC부호기는 코드워드 크기  $n_{ldpc}$ ,  $c=(i_0,i_1,...,i_{k_{ldpc}-1},p_0,p_1,...,p_{n_{ldpc}-k_{ldpc}-1})$  에 정보블록크기  $k_{ldpc}$ ,  $i=(i_0.i_1,...,i_{k_{ldpc}-1})$  를 부호화한다. 코드워드의 전송은  $i_0$ 와  $p_{n_{ldpc}-k_{ldpc}-1}$ 이 주어질 때 시작하고 LDPC 코드 파라메타  $(n_{ldpc}, k_{ldpc})$  는 표 2-3과 표2-4에 주어진다. 표2-3은 long frame 길이인 N=64800일 때의 코딩 파라메타이며, 표2-4는 short frame인 N=16200일 때 코딩 파라메타를 나타낸다.

### 표 2-3. 코딩 파라메타 ( $n_{ldpc} = 64800$ )

Table 2-3. Coding parameter ( $n_{ldpc} = 64800$ )

| LDPC | BCH<br>Uncoded  | BCH coded block $N_{bch}$ LDPC | BCH                   | LDPC<br>Coded    |

|------|-----------------|--------------------------------|-----------------------|------------------|

| Code | Block $k_{bch}$ | Uncoded Block $K_{ldpc}$       | t-error<br>correction | Block $N_{ldpc}$ |

| 1/4  | 16008           | 16200                          | 12                    | 64800            |

| 1/3  | 21408           | 21600                          | 12                    | 64800            |

| 2/5  | 25728           | 25920                          | 12                    | 64800            |

| 1/2  | 32208           | 32400                          | 12                    | 64800            |

| 3/5  | 38688           | 38880                          | 12                    | 64800            |

| 2/3  | 43040           | 43200                          | 10                    | 64800            |

| 3/4  | 48408           | 48600                          | 12                    | 64800            |

| 4/5  | 51648           | 51840                          | 12                    | 64800            |

| 5/6  | 53840           | 54000                          | 10                    | 64800            |

| 8/9  | 57472           | 57600                          | 8                     | 64800            |

| 9/10 | 58192           | 58320                          | 8                     | 64800            |

## 표 2-4. 코딩 파라메타( $n_{ldpc}$ =16200)

Table 2-4. Coding parameter ( $n_{ldpc} = 16200$ )

| LDPC<br>Code | BCH Uncoded Block $k_{\it bch}$ | BCH coded block $N_{bch}$ LDPC Uncoded Block $K_{ldpc}$ | BCH<br>t-error<br>correctio<br>n | Effective LDPC Rate $K_{ldpc}$ /16200 | LDPC<br>Coded<br>Block<br>$N_{ldpc}$ |

|--------------|---------------------------------|---------------------------------------------------------|----------------------------------|---------------------------------------|--------------------------------------|

| 1/4          | 3072                            | 3240                                                    | 12                               | 1/5                                   | 16200                                |

| 1/3          | 5232                            | 5400                                                    | 12                               | 1/3                                   | 16200                                |

| 2/5          | 6312                            | 6480                                                    | 12                               | 2/5                                   | 16200                                |

| 1/2          | 7032                            | 7200                                                    | 12                               | 4/9                                   | 16200                                |

| 3/5          | 9552                            | 9720                                                    | 12                               | 3/5                                   | 16200                                |

| 2/3          | 10632                           | 10800                                                   | 12                               | 2/3                                   | 16200                                |

| 3/4          | 11712                           | 11880                                                   | 12                               | 11/15                                 | 16200                                |

| 4/5          | 12432                           | 12600                                                   | 12                               | 7/9                                   | 16200                                |

| 5/6          | 13320                           | 13320                                                   | 12                               | 37/45                                 | 16200                                |

| 8/9          | 14400                           | 14400                                                   | 12                               | 8/9                                   | 16200                                |

| 9/10         | NA                              | NA                                                      | NA                               | NA                                    | NA                                   |

Fig. 2-9. Performance curves of LDPC with N=16200 according to coding rate

# 제 3 장 이동성 DVB-S2 알고리즘

### 제 3-1 절 FIFTH 제안모델

FIFTH는 Fast Internet for Fast Trains Hosts의 약자로 고속 열차의 승객에게 디지털 텔레비전이나 인터넷 서비스를 제공하기 위함이다. FIFTH는 DVB-S 표준을 기반으로 구성되었다.

### 3.1.1. Train interruption 채널 모델링 방법

다음 그림은 기차 선로의 단면을 나타낸 그림이다.

그림 3-1. 열차 선로 환경

Fig. 3-1. Circumstance of train line

기차가 선로 위를 달릴 때, electronic line supporter에 의해 위성의 신호의 감쇄가 일어나게 되는데, 그 때의 신호의 상태는 그림 3-2와 같고, electronic line supporter의 주기인 50m마다 신호의 감쇄가 발생한다.

그림 3-2. Train interruption 감쇄

Fig. 3-2. Attenuation by train interruption

기차의 속도가 300 km/h라고 한다면 다음 식 3.1과 같이 속도의 단위를 m/s로 나타낼 수 있다.

$$300km/h = \frac{300 \times 10^3 m}{60m \times 60s} = 83.333m/s \tag{3.1}$$

즉, 기차는 1초에 83.333m를 진행한다. 따라서 electronic line supporter의 영향을 받지 않는 구간의 시간은 다음 식 3.2와 같이 계산될 수 있다.

$$1s:83.333m = xs:49.5m$$

$$x = 0.594s$$

(3.2)

그리고 electronic line supporter의 영향을 받는 구간의 시간은 식 3.3

의 방법과 같이 계산할 수 있다.

$$1s:83.333m = xs:0.5m$$

$$x = 0.006s$$

(3.3)

데이터의 속도를 5Mbps라고 한다면 electronic line supporter의 영향을 받지 않는 구간의 데이터 량은 다음 식 3.4와 같다.

$$5 \times 10^6 bit : 1s = xbit : 0.6s$$

$x = 3 \times 10^6 bit$  (3.4)

또한 electronic line supporter의 영향을 받는 구간의 데이터 량은 다음 식 3.5와 같다.

$$5 \times 10^{6} bit : 1s = xbit : 0.006s$$

$$x = 30 \times 10^{3} bit$$

(3.5)

electronic line supporter에 의한 burst 에러를 정정하기 위하여 interleaver를 시스템에 첨가할 수 있는데, FIFTH에서는 다음과 같이 크게 2가지 방법을 제안하고 있다.

### 3.1.2. FIFTH 제안모델 I

이 방법은 기존의 DVB-S2 시스템의 FEC encode와 mapping 사이에 interleaver를 첨가하는 방법이다. interleaver를 첨가함으로써 electronic line supporter에 의한 burst 에러들은 FEC decoder에 들어가기 전에 분산되어 FEC decoder가 에러를 정정할 수 있게 된다. 따라서 decoder를 여러 개 붙이지 않고서도 burst 에러를 정정할 수 있다.

그림 3-3. FIFTH 제안모델 I

Fig. 3-3. Proposed model I by FIFTH

그러나 decoding 알고리즘에 신뢰성이 있는 수신 신호를 주어야 하므로 de-interleaver는 연판정 데이터를 decoding 알고리즘에 주어야 하고, de-interleaver 메모리는 interleaver의 m배만큼, 즉 연판정된 데이터의 비트 수만큼 커야 한다. 또한 내부 채널 interleaver의 채택은 DVB-S2 프레임 구조를 기반으로 한 동기 알고리즘을 요구하므로 채널 인코더를 적용하기 위해서는 DVB-S2 표준을 수정해야 한다는 단점이 있다.

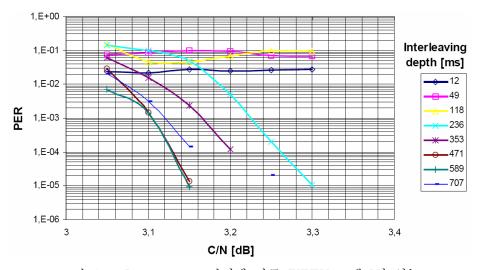

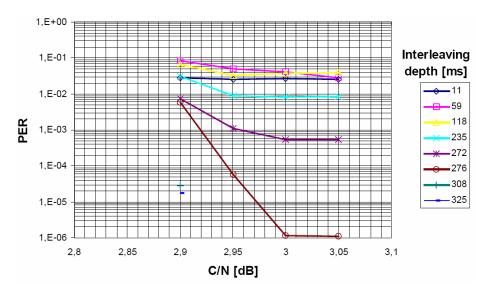

그림 3-4. Interleaving 길이에 따른 FIFTH 모델 I의 성능

Fig. 3-4. Performance of FIFTH model I by interleaving depth

### 3.1.3. FIFTH제안 모델 II

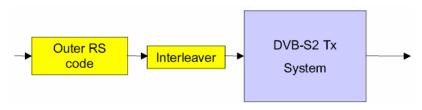

그림 3-5. FIFTH제안 모델 II

Fig. 3-5. Proposed model II by FIFTH

이 방법은 DVB-S2 시스템의 앞 단에 외부 부호(RS 코드)와 interleaver를 연결하여 구현 가능하므로 DVB-S2와의 충돌되는 점을 적게 할 수 있다는 장점이 있다. interleaver와 de-interleaver의 입, 출력 값은 강판정 된 값인 '0'과 '1'이다.

그러나 DVB-S2 시스템에 외부 부호를 적용함으로써 이전의 DVB-S2 시스템보다 대역 효율이 떨어진다는 단점이 있다.

이 모델에는 다음과 같은 네 가지의 방식으로 제안되어 있다. 이를 표 3-1에 요약하였다.

표 3-1. FIFTH 제안모델 사양

Table. 3-1. Proposed model II option

| DVE        | 3-S2             | DC Coding Data |

|------------|------------------|----------------|

| Modulation | LDPC Coding Rate | RS Coding Rate |

| QPSK       | 2/3              | 1023,975,48    |

| QPSK       | 3/4              | 255,191,64     |

| QPSK       | 3/4              | 233,191,32     |

| QPSK       | 2/3              | 209,191,17     |

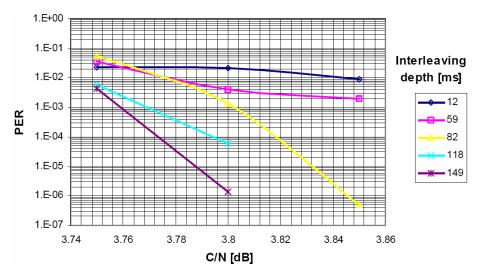

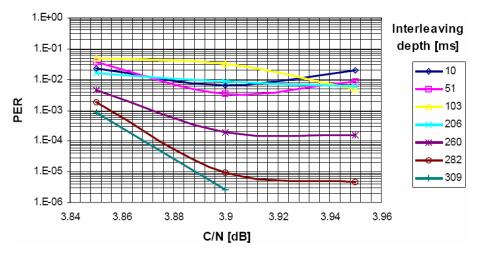

그림 3-6, 3-7, 3-8, 3-9는 FIFTH 제안 모델 II에 대한 FIFTH에서 평가한 성능곡선이다.

그림 3-6. QPSK + 2/3 + RS(1023,975,48)

Fig. 3-6. QPSK + 2/3 + RS(1023,975,48)

그림 3-7. QPSK + 3/4 + RS(255,191,64)

Fig. 3-7. QPSK + 3/4 + RS(255,191,64)

그림 3-8. QPSK + 3/4 + RS(223,191,32)

Fig. 3-8. QPSK + 3/4 + RS(223,191,32)

그림 3-9. QPSK + 2/3 + RS(209,191,18)

Fig. 3-9. QPSK + 2/3 + RS(209,191,18)

## 제 3-2 절 DVB-S2M 제안 모델

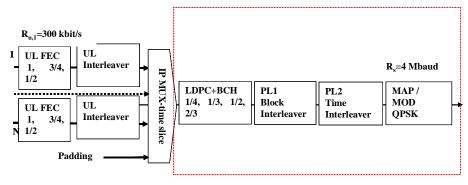

DVB-S2M에서 제안한 시스템 블록 다이어그램은 다음 그림 3-10과 같다.

그림 3-10. DVB-S2M 제안 모델

Fig. 3-10. Proposed model by DVB-S2M

여기에서 UL FEC는 RS 부호이고 UL interleaver는 virtual interleaver, PL1은 Block interleaver, PL2는 Time interleaver을 나타낸다. 시스템 블록 다이어그램의 interleaver에 대하여 다음에서 자세히 설명하다.

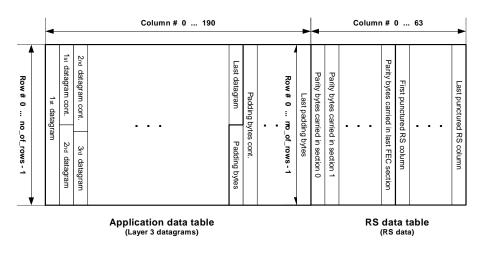

### 3.2.1. Virtual Interleaver

그림 3-11은 MPE-FEC 프레임을 나타낸다. Frame을 구성하는 하나의 심벌은 8비트로 구성되며, column의 개수는 255개의 심벌로 고정되어 있고, column의 길이는 최고 1024개의 심벌까지 유동적으로 설정 가능하다. 다시 말하자면 row의 길이는 255심벌로 고정되어 있고, row의 개수는 최고 1024개의 심벌까지 유동적으로 설정 가능하다. 따라서 총 프레임의 크기는 최대 약 2M 비트를 가질 수 있다.

191개의 심벌로 이루어진 프레임 왼쪽의 부분은 정보 비트 부분이고, 64개의 심벌로 이루어진 프레임의 오른쪽 부분은 RS 부호화 과정으로 생

겨난 RS 패리티 부분이다.

데이터가 입력되면 프레임의 가장 왼쪽에 위치한 column을 채우면서 오른쪽 방향의 column에 데이터를 저장하고, 저장되지 않은 부분이 생긴다면 이 부분은 '0'으로 채워 넣는다.

데이터를 모두 저장하고 난 후에, row 단위로 RS 부호화를 실행한다. 191개의 데이터 심벌을 이용하여 64 심벌의 RS 패리티를 만든다. 부호화가 끝난 데이터는 column 방향으로, 즉, 가장 왼쪽의 column부터 가장 오른쪽의 column까지 블록에 입력된 순서 차례대로 전송된다.

그림 3-11. MPE-FEC 프레임 구조

Fig. 3-11. MPE-FEC frame construction

RS 부호화 과정의 전후로 하여 interleaver와 de-interleaver 과정을 수행하지만, 프레임으로 입력되는 순서와 출력되는 순서가 같아 가시적으로 interleaver 과정이 들어나지는 않기 때문에 이를 'virtual interleaver'라고한다.

### 3.2.2. Time Interleaver

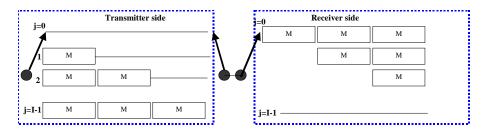

그림3-12는 Forney가 제안한 time interleaver의 모습으로, 여기서 I는

interleaver의 depth이고 M은 레지스터가 가지고 있는 저장 장소 하나의 크기로 LDPC의 데이터 길이(N=16200)를 I로 나눈 값과 같다(M = 16200/I). 그리고 j는 time interleaver의 인덱스이다

그림 3-12. PL#2 time interleaving

Fig. 3-12. PL#2 time interleaving

비트 열이 들어오면 순서대로 레지스터에 저장이 되는데 이어지는 레지스터에는 그 이전의 레지스터보다 하나 더 많은 저장 장소가 있다. 여기에서 첫 번째 레지스터에는 저장 장소가 없어 데이터가 바로 전송된다. 레지스터는 FIFO (first input first output) 레지스터이다. 따라서 각 인덱스에는 인덱스 수만큼의 저장 장소가 있다.

새로운 데이터가 레지스터에서 나오면 정류자(commutator)는 다음 레지스터로 스위치를 옮기게 되고 그 레지스터에서 가장 오래된 값이 출력된다. 정류자가 I-1 번째 레지스터 후에 정류자는 다시 0번째 레지스터로 돌아가서 다시 시작한다.

Time de-interleaver의 모양은 time interleaver와 정반대이므로 de-interleaving 과정도 time interleaver의 역 과정을 수행하게 된다. 따라서 j=0번째 열의 레지스터가 I-1개로 가장 긴 저장 장소를 가지고 있고 j=I-1 번째의 레지스터는 저장 장소를 가지고 있지 않다.

I와 M의 크기는 다음 표3-2와 같이 8개 중 하나로 설정할 수 있다.

신호가 interleaver와 de-interleaver에 각 레지스터의 차례대로 저장되고 정류자에 의하여 출력되는데 각 레지스터에는 저장 공간이 있어 지연시간이 발생하게 되고, 지연시간은 다음 식 3-6과 같이 계산할 수 있다

$$I \times (I-1) \times M \tag{3-6}$$

Interleaver 후의 신호는 앞과 뒤에 지연시간이 나뉘어 있지만 de-interleaver 후의 신호는 신호의 앞부분에  $I \times (I-1) \times M$  만큼의 지연시간이 생기고 그 다음부터는 신호가 지연 없이 차례대로 출력되게 된다.

표 3-2. PL#2 time interleaving 사양

Table 3-2. Option for PL#2 time interleaving

| I=1         | I=2    | I=5    | I=10   |

|-------------|--------|--------|--------|

| No time Int | M=8100 | M=3240 | M=1620 |

| I=20        | I=40   | I=81   | I=162  |

| M=810       | M=405  | M=200  | M=100  |

#### 제 3-3 절 제안한 Interleaver 모델

DVB-S2M에서는 2장 1절에서 언급된 DVB-T규격의 bit interleaver와 symbol interleaver를 결합한 interleaver를 block interleaver로써 사용한다. Bit interleaver를 사용하기 위해서는 LDPC 부호의 N = 16200개의 데이터를 하나의 bit interleaver에서 126개로 나누어 분리하여야 하는데, 16200개의 데이터는 126으로 나누어 떨어지지 않아 72개의 데이터가 남게 되어 126bit를 만족하기 위해서는 54개의 "null" 데이터를 첨가해야 하고 출력되는 비트 수는 16254개이다. 결과적으로 이러한 임의의 "null" 데이터 삽입으로 전송 효율을 1.003배 저하시키는 결과를 초래한다.

Symbol interleaver를 사용하기 위해서는 주소를 발생시키는 주소 발생기가 필요하므로 복잡한 회로가 필요하게 된다.

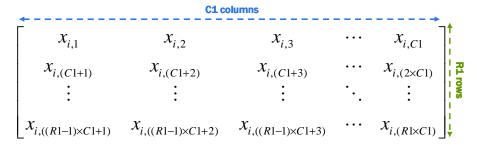

따라서 본 논문에서는 이러한 회로 구현이 필요하지 않고, LDPC 부호어의 길이(N = 16200)에 적합한 block interleaver를 제안하고, 이를 그림 3-13에 나타내었다.

제안하고자 하는 block interleaver는 그림 3-13과 같이 수행된다. 입력비트 열은  $x_{i,1}, x_{i,2}, ..., x_{i,X_i}$ 로 표현할 수 있고,  $X_i$ 는 의 데이터 길이 (N=16200)와 같다.

그림 3-13. PL#1 block interleaving 구조

Fig. 3-13. PL#1 block interleaving construction

Row의 개수 R1은 LDPC의 데이터 길이(N=16200)를 column의 개수로 나눈 값이다. 데이터 열이 입력되면 가장 위쪽의 row부터 가장 아래의 row까지 차례대로 블록에 데이터를 저장한다. 블록이 데이터로 완전히 채워진 뒤, 한 번에 하나의 column이 출력된다. 출력 될 때는 다음 표에 나타난 것과 같이 inter-column permutation patterns에 따라 각 column이 출력된다.

Block de-interleaver는 block interleaver의 역 과정으로 수행하면 된다. 수신된 데이터 열을 inter-column permutation patterns에 따라 그에 해당하는 column에 차례로 저장한 후 가장 위쪽의 row부터 가장 아래의 row까지 차례로 데이터를 출력하면 된다.

제안하고자 하는 block interleaver는 표 3-3에서 나타난 바와 같이 4 가지의 사양이 있다.

$C_1$ 의 길이가 1이라면 이는 interleaving효과를 주지 않는 것이고, 2, 4, 8의 경우에는 "Inter-column Permutation Patterns"의 순서에 따라 데이터를 배치하여 interleaving 한다.

표 3-3. PL#1 block interleaver 사양

Table 3-3. Option for PL#1 time interleaving

| TTI  | Nimber of Columns C <sub>1</sub> | Inter-column Permutation Patterns <\P1_{C1(0)},, P1_{C1(C1-1)}> |

|------|----------------------------------|-----------------------------------------------------------------|

| 10ms | 1                                | 0                                                               |

| 20ms | 2                                | 0,1                                                             |

| 40ms | 4                                | 0,2,1,3                                                         |

| 80ms | 8                                | 0,4,2,6,1,5,3,7                                                 |

# 제 4 장 시뮬레이션 및 성능 평가

이 장에서는 앞에서 설명한 DVB-S2M를 토대로 시뮬레이션 하였다. 시뮬레이션에서 사용한 RS 부호는 RS(255,191,64)이고, LDPC는 부호화 율이 1/2인 short LDPC를 사용하였다.

그리고 4-2절에서는 기존의 bit interleaver와 제안한 block interleaver의 성능을 비교 분석하였고, 4-3절과 4-4절에서 각 채널 상태에 따라 RS 부호와 LDPC 부호의 사용 유무, 세 가지 interleaver의 사용 유무, 그리고 time interleaver와 block interleaver의 크기를 변경하면서 시뮬레이션 하였고, virtual interleaver를 사용하였을 경우, virtual interleaver의 크기는 512로 고정하여 시뮬레이션 하였다.

#### 제 4-1 절 시뮬레이션 채널 환경

채널 환경은 Gaussian 채널 환경과 train interruption 채널 환경을 설정하였다. 여기서 train Interruption에 의한 에러의 길이는 13000 bits로 설정하여 시뮬레이션 하였는데, 그 이유는 여기에서 사용된 RS 코드의 에러정정 능력은 32bytes이고, virtual interleaver의 크기는 512이기 때문에에러의 길이를  $32 \times 8 \times 512 = 131072$ 로 가정하여 시뮬레이션 하였다.

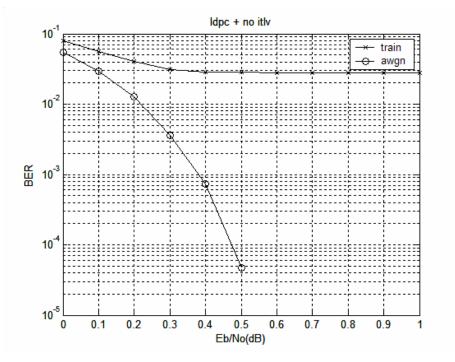

그림 4-1. AWGN과 TI환경에서 DVB-S2 성능평가

Fig. 4-1. Performance of DVB-S2 under AWGN and TI

그림 4-1은 train interruption 환경과 AWGN에서 DVB-S2 규격의 LDPC 부호만 이용하여 성능을 평가한 곡선이다. Train interruption 환경에서 LDPC 부호의 성능이 현저히 떨어짐을 알 수 있다. 따라서 UL의

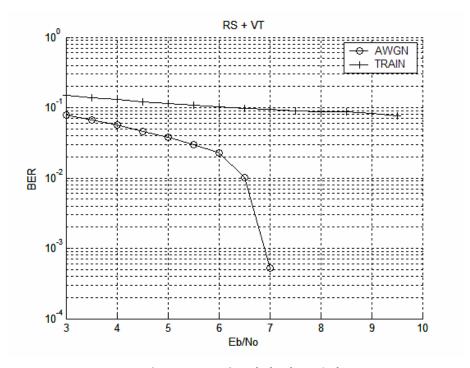

그림 4-2. UL 부호방식 성능 분석

Fig. 4-2. Performance of UL coding scheme

그림 4-2에서 보는 바와 같이 train interruption 환경에서 RS 부호는 단독으로 에러를 정정할 수 없음을 알 수 있다. 여기에서 virtual interleaver를 사용한 이유는 train interruption 에러를 RS 코드가 정정할 수 있도록 분산시키기 위해서이다.

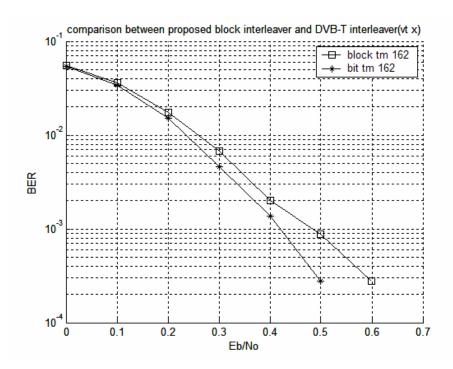

# 제 4-2 절 기존의 block interleaver와 제안된 block interleaver의 성능 비교

DVB-S2M에서는 2장 1절에서 언급된 DVB-T규격의 bit interleaver와 symbol interleaver를 결합한 interleaver를 block interleaver로써 사용한다. Bit interleaver를 사용하기 위해서는 LDPC 부호의 N = 16200개의 데이터를 하나의 bit interleaver에서 126개로 나누어 분리하여야 하는데, 16200개의 데이터는 126으로 나누어 떨어지지 않아 임의의 "null" 데이터를 삽입해야 하므로 이는 전송 효율을 저하시키는 결과를 초래한다. 또한 symbol interleaver를 사용하기 위해서는 주소를 발생시키는 주소 발생기가 필요하므로 복잡한 회로가 필요하게 된다.

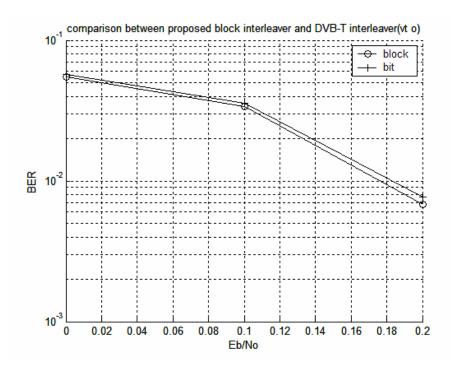

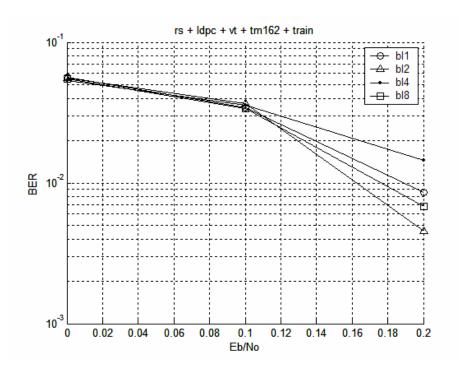

기존의 block interleaver와 제안한 block interleaver의 성능을 그림 4-3에 비교하였다. 그 결과 성능이 비슷하므로 기존의 block interleaver보다는 제안된 block interleaver가 구현 측면에서 더 효율적임을 알 수 있다.

그림 4-3. 기존의 block interleaver와 제안한 block interleaver의 성능비

(RS(255,191,64), LDPC(R=1/2), time interleaver depth 162, train interruption)

Fig. 4-3. Performance comparison between proposed block interleaver and DVB-T interleaver

(RS(255,191,64), LDPC(R=1/2), time interleaver depth 162, train interruption)

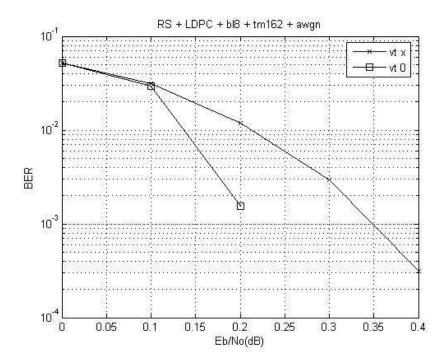

그림 4-4. 기존의 block interleaver와 제안한 block interleaver의 성능비

(RS(255,191,64), LDPC(R=1/2), virtual interleaver, time interleaver depth 162, train interruption)

Fig. 4-4. Performance comparison between proposed block interleaver and DVB-T interleaver

(RS(255,191,64), LDPC(R=1/2), virtual interleaver, time interleaver depth 162, train interruption)

# 제 4-3 절 AWGN 채널 환경에서 성능 평가

본 절에서는 AWGN 채널 환경 하에서 RS 코드와 LDPC 코드의 유무, time interleaver와 block interleaver의 크기를 변경하면서 성능 평가를 하였다.

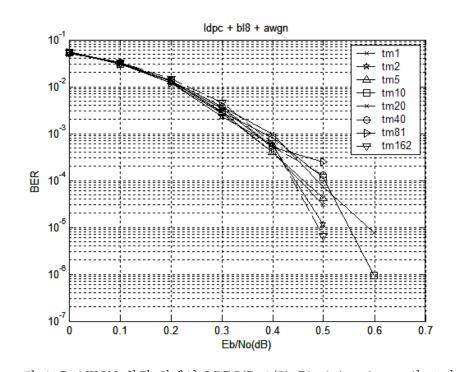

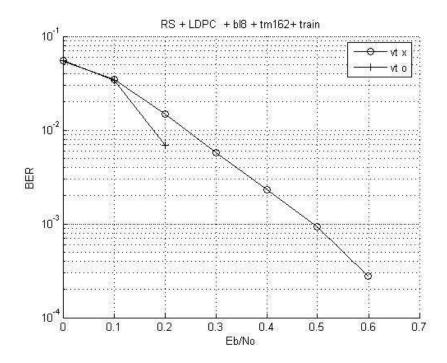

그림 4-5. AWGN 환경 하에서 LDPC(R=1/2), Block interleaver의 크기가 8 일 때, time interleaver 크기에 따른 성능

Fig. 4-5. Performance according to time interleaver depth under AWGN (LDPC(R=1/2), block interleaver size 8)

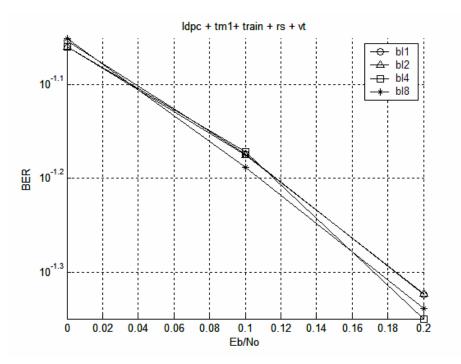

그림 4-6. AWGN 환경 하에서 LDPC(R=1/2), time interleaver 크기 162 일 때, block interleaver의 크기에 따른 성능

Fig. 4-6. Performance according to block interleaver size under AWGN (LDPC(R=1/2), time interleaver depth 162)

그림 4-7. AWGN 환경 하에서 RS(255,191,64), LDPC(R=1/2), block interleaver의 크기 8, time interleaver의 크기 162 일 때, virtual interleaver 유무에 따른 성능

Fig. 4-7. Performance whether virtual interleaver exists or not under AWGN (RS(255,191,64), LDPC(R=1/2), block interleaver size 8, time interleaver depth 162)

그림 4-8. AWGN 환경 하에서 RS(255,191,64), LDPC(R=1/2), block interleaver의 크기 8, virtual interleaver가 존재할 때, time interleaver의 크기에 따른 성능

Fig. 4-8. Performance according to time interleaver depth under AWGN (RS(255,191,64), LDPC(R=1/2), block interleaver size 8, time interleaver depth 162, virtual interleaver)

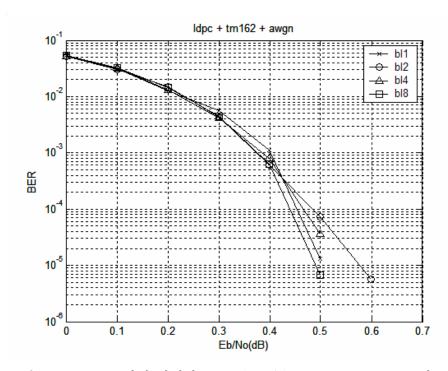

그림 4-9. AWGN 환경 하에서 RS(255,191,64), LDPC(R=1/2), virtual interleaver 존재, time interleaver의 크기 162일 때, block interleaver의 크기에 따른 성능

Fig. 4-9. Performance according to block interleaver size under AWGN (RS(255,191,64), LDPC(R=1/2), time interleaver depth 162, virtual interleaver)

# 제 4-4 절 TI(Train Interruption) 환경 하에서 성능 평가

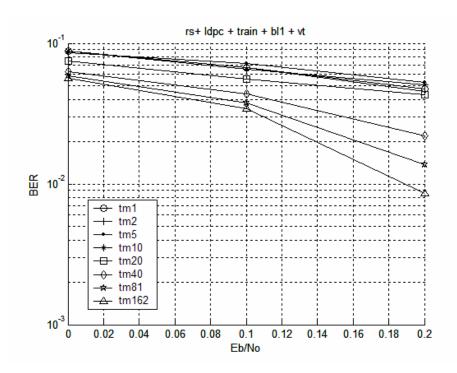

본 절에서는 train Interruption 채널 환경 하에서 RS 코드와 LDPC 코드의 유무, time interleaver와 block interleaver의 크기를 변경하면서 성능 평가를 하였다.

그림 4-10. Train interruption 환경 하에서 LDPC(R=1/2), time interleaver 크기 162 일 때, block interleaver 개수에 따른 성능 Fig. 4-10. Performance according to block interleaver size under train interruption (LDPC(R=1/2), time interleaver depth 162)

interleaver 크기 8일 때, time interleaver의 크기에 따른 성능

Fig. 4-11. Performance according to time interleaver depth under train interruption (LDPC(R=1/2), block interleaver size 8)

그림 4-12. Train interruption 환경 하에서 RS(255,191,64), LDPC(R=1/2), Block interleaver의 크기 8, time interleaver의 크기 162 일 때, virtual interleaver 유무에 따른 성능

Fig. 4-12. Performance whether virtual interleaver exists or not under train interruption

(RS(255,191,64), LDPC(R=1/2), block interleaver size 8, time interleaver depth 162)

그림 4-13. Train interruption 환경 하에서 RS(255,191,64), LDPC(R=1/2), virtual interleaver, block interleaver 크기 1일 때, time interleaver의 크기에 따른 성능

Fig. 4-13. Performance according to block interleaver size under train interruption (RS(255,191,64), LDPC(R=1/2), time interleaver depth 1, virtual interleaver)

그림 4-14. Train interruption 환경 하에서 RS(255,191,64), LDPC(R=1/2), block interleaver의 크기 1, virtual interleaver가 존재할 때, time interleaver의 크기에 따른 성능

Fig. 4-14. Performance according to time interleaver depth under train interruption (RS(255,191,64), LDPC(R=1/2), block interleaver size 1, virtual interleaver)

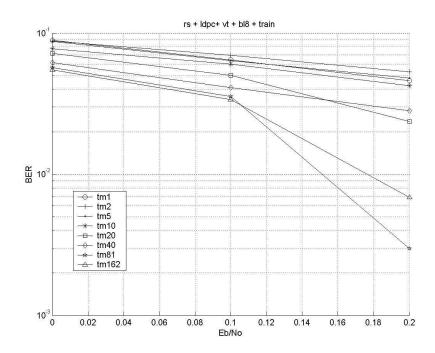

그림 4-15. Train interruption 환경 하에서 RS(255,191,64), LDPC(R=1/2), virtual interleaver 존재, block interleaver 크기 8일 때, time interleaver의 크기에 따른 성능

Fig. 4-15. Performance according to time interleaver depth under train interruption (RS(255,191,64), LDPC(R=1/2), block interleaver size 8, virtual interleaver)

그림 4-16. Train interruption 환경 하에서 RS(255,191,64), LDPC(R=1/2), time interleaver가 162일 때 block interleaver 크기에 따른 성능

Fig. 4-16. Performance according to block interleaver size under train interruption (RS(255,191,64), LDPC(R=1/2), time interleaver depth 162, virtual interleaver)

# 제 5 장 결 론

차세대 위성통신은 소형 이동형 지상파 방송 및 고정형 지상파 방송을 위성과의 융합에 관한 연구가 활발히 진행 중에 있으며, 특히 위성을 이용한 쌍방향 통신, 즉 무선 인터넷과의 융합, 이동체에 대한 위성 방송 및 인터넷 통신을 하기 위한 연구가 제안되고 있다. 전세계적으로 FIFTH (Fast Internet for Fast Train Host) 프로젝트가 현재 이동체 위성 방송분야에연구가 활발히 진행되고 있다. 이의 연구를 위해서는 우수한 성능을 만족하면서 가입자가 이동을 하더라도 지속적으로 방송을 제공하기 위해서는 DVB-S2 표준화 등에서 논의되고 있는 LDPC (Low Density Parity Check) 부호와 interleaver, 외부 부호의 결합한 새로운 코딩방식의 연구가 필수적이며, 본 논문에서도 이를 중점적으로 연구 및 시뮬레이션을 통한 성능 평가를 하였다. 이의 정확한 성능 평가를 위해서는 DVB-S2 시스템과 이동체에 대한 통신 규격인 DVB-T, DVB-H를 결합한 이동체에 대한 위성 방송, 위성인터넷 통신을 위해 채널 모델링, 이동중인 물체의 속도, 터널에서의 deep fading환경에서도 통신이 가능한 interleaver 의 구조 등을 연구하였다.

따라서 본 논문에서는 DVB-S2를 근간으로 하는 LDPC의 Short frame 의 적용을 기본으로 할 때, 즉, HNS사에서 제시한 LDPC 각 부호화율과 QPSK변조기법으로 통신한다고 가정할 때, DVB-H의 MPE-FEC, DVB-T의 전공 모델인 block interleaver 를 결합한 이동체 위성통신을 위한 채널 부호화 기법에 대한 성능분석을 하였다. 기존의 DVB-S2시스템에 외부부호로는 RS부호와 virtual interleaver 기법의 첨가와 내부 부호로는 DVB-S2의 LDPC부호와 내부 interleaving, 즉 block interleaver 와 convolutional interleaver 의 존재에 각 파라미터를 변화 시켜가면서 성능분석을 하였다. Deep fading 채널의 묘사는 train interruption이라 가정할때 외부 부호는 성능에 영향을 미치고 있으며, 내부 부호에서의 LDPC 부호 또한 성능에 영향을 미치는 요소라 분석 된다.

본 논문에서는 기차의 electronic line supporter에 의한 신호의 감쇄를 고려하여 시뮬레이션 하였다.

DVB-S2M에서 제안한 block interleaver는 DVB-T 규격의 bit interleaver와 symbol interleaver를 결합한 형태를 block interleaver로써 사용한다. 그러나 bit interleaver를 사용하기 위해서는 LDPC 부호의 N = 16200개의 데이터를 하나의 bit interleaver에서 126개로 나누어 분리하여야 하는데, 16200개의 데이터는 126으로 나누어 떨어지지 않아 임의의 "null" 데이터를 삽입해야 하므로 이는 전송 효율을 1.003배 저하시키는 결과를 초래한다. 또한 symbol interleaver를 사용하기 위해서는 주소를 발생시키는 주소 발생기가 필요하므로 복잡한 회로가 필요하게 된다. 그러므로 본 논문에서는 기존의 block interleaver보다 구현이 쉬운 block interleaver를 제안하였다. 시뮬레이션 결과 성능은 비슷하지만 구현 측면에서 보았을 때 효율적임을 알 수 있다.

### 참고문헌

- [1] "Satellite Broadcasting System of Integrated Service Digital Broadcasting", *ITU-R* BO.1227-2

- [2] ETSI EN 301 210: "Digital Video Broadcasting (DVB): Framing Structure, Channel Coding and Modulation for Digital Satellite News Gathering (DSNG) and Other Contribution Applications by Satellite". (DVB-S2)

- [3] ETSI EN 300 744: "Digital Video Broadcasting (DVB): Framing Structure, Channel Coding and Modulation for Digital Terrestrial Television." (DVB-T)

- [4] ETSI EN 302 304: "Digital Video Broadcasting (DVB); Transmission System for Handheld Terminal." (DVB-H)

- [5] Shigeo Nakajima, "Adaptive Coding Rate Trellis-coded 8PSK System," IEICE Trans. FUND- AMENTALS, Vol. E80-A, No. 7, July, 1997.

- [6] A. Hashimoto, et al, "Development of a Transmission System and an Integrated Receiver for Satellite," ISDB IEEE Transaction on Consumer Electronics, Vol. 43 p.337~343 August, 1997

- [7] H. Katoh, et al, "A Flexible Transmission Technique for the Satellite ISDB Systems", *IEEE Transmissions on Broadcasting*, Vol. 42. vol. 3, September.1996

- [8] N. Kawai, et al, "Performance of Multimedia Broadcasting Through ISDB Transmission System", *IEEE Transaction on Broadcasting*, Vol.42, No.3, p151~158, Sep, 1996

- [9] Y. Nishida, et al, "Development of an HDTV codec conforming to MPEG-2 MP@HL and its picture quality", ITE of Japan Tech. Rep., Vol 21, No. 30, p31~36 BCS' 97-22, BFO'97-37, May, 1997

- [10] K. Ohsaki, et al, "Transmission Structure of Digital Broadcasting", 1994 International Conference on COMMUNICATIONS, 326.2 May, 1994

- [11] R. G. Gallager, "Low-Density Parity-Check Codes," *IRE trans.information theory*, vol.8, pp.21-28, 1962.

- [12]D. J. C. Mackay and R. M. Neal, "Near Shannon Limit Performance of Low-Density Parity-Check Codes," *Electron. Letter*, Vol.32, pp. 1645-1646, Aug, 1996.

- [13]M. Sipser and D. A. Spielman, "Expander Codes," IEEE Trans. Information

- Theory, vol.42, pp.1720-1722, Aug. 1996

- [14]T. Richardson and R. Urbanke, "Efficient Encoding of Low-Density Parity Check Codes," *IEEE Trans. Information Theory*, vol. 47, pp. 638-656, Feb.2001

- [15]J. W. Bond, S. Hui, and H. Schmidt, "Constructing low-density parity-check codes," EUROCOMM 2000, Information Systems for Enhanced Public Safety and security. IEEE/AFCEA, pp.260-262, 2000.

- [16] David J. C. Mavkay "Good Error-Correcting Codes Based on Very Sparse Matrics" *IEEE Trans. Information Theory*, vol. 45, NO. 2. March 1999.

- [17] Forney, G.D., "Burst-Correcting Codes for the Classic Bursty Channel," *IEEE*, *trans. Commun. Technol.*, vol. COM-19, pp.772-781, Oct. 1971.

- [18] W. T. Webb and L. Hanzo, Modern Quadrature Amplitude Modulation, Pentech Press, 1994.

# 감사의 글

대학생활 4년과 대학원 생활 2년 동안 저를 끊임없이 지도해주신 정지원 교수님께 제일 먼저 감사의 인사를 드리고 싶습니다. 첫 여자제자이기에 교수님께서 제게 신경을 많이 써 주셨는데, 제게 신경 써 주신 것보다 못해왔다는 생각이 듭니다. 그렇지만, 앞으로 발전하는 모습을 보이도록 노력해 나가겠습니다. 학문적인 가르침은 물론이거니와 인생에 있어서의 가르침들을 가지고 살겠습니다. 앞으로도 지켜봐 주실 거죠~?

연구실에 처음 들어왔을 때부터 지금까지 함께한 연구실 사람들도 고마 워요. 모르는 것을 물어볼 때 귀찮아 하지 않은 다른 연구실 오빠들~!!! 제 가 고마워 하는 거 아시죠?

내 생활과 인생의 vitamin, 친구들 정말 고마워~^^\*.

어려운 환경에서도 막내딸이 하고 싶어하는 공부 계속시켜주시느라 힘이 드셨을 텐데......

아빠, 엄마 정말 고마워요♥ 쩡유니도 고맙고~^^

마지막으로 지금부터 영원까지 저와 함께하시는 하나님께 이 영광을 돌리고 싶습니다.